MTD(Memory Technology Device) -1-

MTD는 플래시 메모리를 상위 application 계층과 연결시켜 소통하기 위한 별도 계층의 디바이스 파일이다.

- 고전(Traditinal) 리눅스의 블럭 디바이스나 캐릭터 디바이스만으로는 플래시 메모리와 communication하는 것이 어울리지 않는다.

- 캐릭터 디바이스는 seek를 지원하지 않는다.

- 블럭 디바이스는 write와 erase를 구분하지 않는다.

- 플래시 메모리를 위해 별도의 디바이스인 MTD 디바이스가 필요해졌다.

- UBIFS 파일 시스템은 UBI를 통해 MTD 디바이스와 연결된다.

- /dev/mtdN

- Block layer 기반으로 동작하는 JFFS2, YAFFS 등과 같은 플래시 파일시스템에 연결시킬 수도 있다.

- 블럭디바이스와 연결할 때 사용되는 디바이스 파일: /dev/mtdblockN

- removal이 가능한 MMC, SD Flash 등도 플래시 메모리 유형에 들어가지만 MTD에 속하지 않고 다른 레이어인 FTL(Flash Translantion Layer)를 사용한다.

MTD 지원 디바이스

- NAND 플래시

- 일반 NAND로 다른 기술을 가진 NAND와 분류하기 위해 Bare NAND, Raw NAND 또는 Pure NAND로 불리기도 한다.

- ECC는 부트 로더 또는 리눅스 커널 드라이버 등의 software로 처리하지만, ECC 기능이 내장된 NAND controller가 사용된 경우 hardware 기능을 사용할 수도 있다.

- NOR 플래시

- ECC가 없는 NOR 플래시

- 희귀하지만 ECC가 있는 NOR 플래시 제품도 있다.

- ECC가 없는 NOR 플래시

- ECC Free NAND

- One NAND

- Nand 플래시 셀에 일부를 Nor 플래시와 연결하여 동작시키고, SRAM과 로직(ECC Controller)을 추가하여 하나의 칩으로 만든 퓨전 메모리이다.

- 삼성이 개발하였으며 도시바 및 몇 개 기업에 라이센스 하였다.

- Nand 플래시 셀에 일부를 Nor 플래시와 연결하여 동작시키고, SRAM과 로직(ECC Controller)을 추가하여 하나의 칩으로 만든 퓨전 메모리이다.

- Flex-One NAND

- One NAND 기능은 동일하고, NAND 플래시의 셀 부분을 MLC를 사용하고 외부에 연결된 부분만 SLC로 구성하여 대용량화 시킨 제품이다.

- ClearNAND

- Micron이 개발하였으며 BA NAND 종류로 ECC 처리를 위해 NAND 칩에 내장된 ECC controller가 ECC 처리를 직접 수행한다.

- LBA NAND

- Toshiba가 개발하였으며 FTL 로직을 NAND 칩에 모두 내장시켜 점점 복잡해지는 호스트 컨트롤러 및 software의 처리를 단순화시켜주는 장범이 있다.

- One NAND

참고: Micron 일부 플래시 칩에 ECC 기능이 내장된 칩들을 위해 리눅스 커널의 메인 라인 v4.13-rc1에서는 On-die NAND 기능을 추가하였다. 삼성은 One NAND 처리를 위해 별도의 서브 트리를 사용한다.

플래시 표준 규격

- JEDEC(Joint Electron Device Engineering Council) 솔리드 스테이트 기술 협회

- 플래시 업계의 1위 및 2위인 삼성과 도시바가 참가한다.

- ONFI(Open Nand Flash Interface)

- 삼성과 도시바를 제외한 나머지 플래시 제조사가 참가한다.

- 기타

- 규격이 정해지기 전에 생산된 제품들(Old none-CFI)

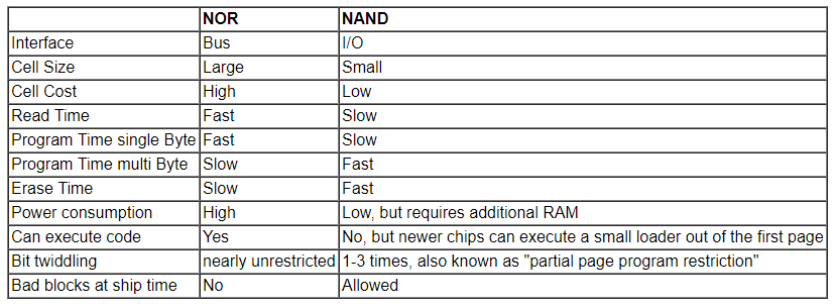

Nor Flash vs Nand Flash

비교

- Bus

- CPU에서 직접 주소가 가능한 방식이라 Bus라고 불린다.

- Nand는 페이지별로 읽기/쓰기 동작을 별도로 해야 한다.

- Cell Size

- 1개의 셀 사이즈가 작게만들 수록 집적화가 커 제한된 면적에서 더 큰 용량을 만들 수 있다.

- NOR 플래시 용량은 2019년 현재 1Mb ~ 1Gb 이다.

- NAND 플래시 용량은 SLC Nand 칩 기준 2019년 현재 1Mb ~ 16Gb 이다.

Parellel vs Serial 방식

처음 NOR 플래시 및 NAND 플래시는 Pararell 방식으로 만들어졌지만 Serial 방식을 쓰는 SPI 버스에 연결할 수 있는 방식도 사용한다. SPI-NAND 및 SPI-NOR 플래시는 Throughput은 약간 떨어지지만 핀 수가 줄어들어 소형으로 만들 수 있는 장점이 있다.

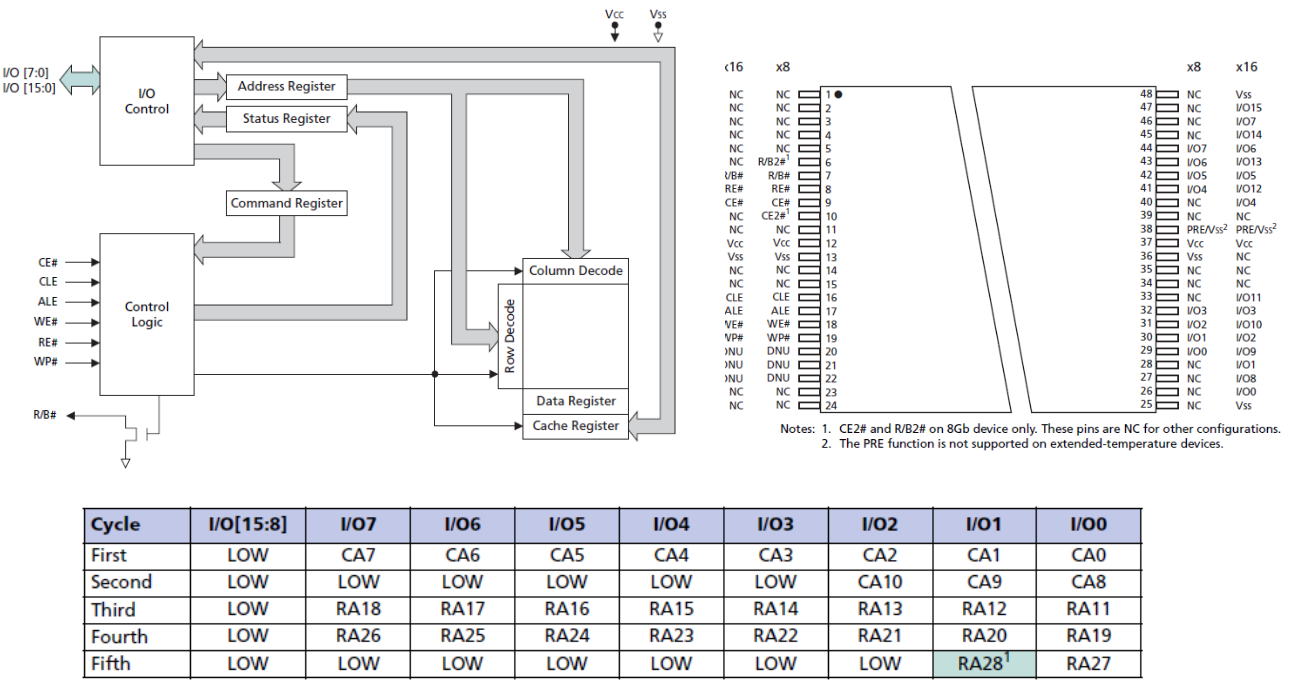

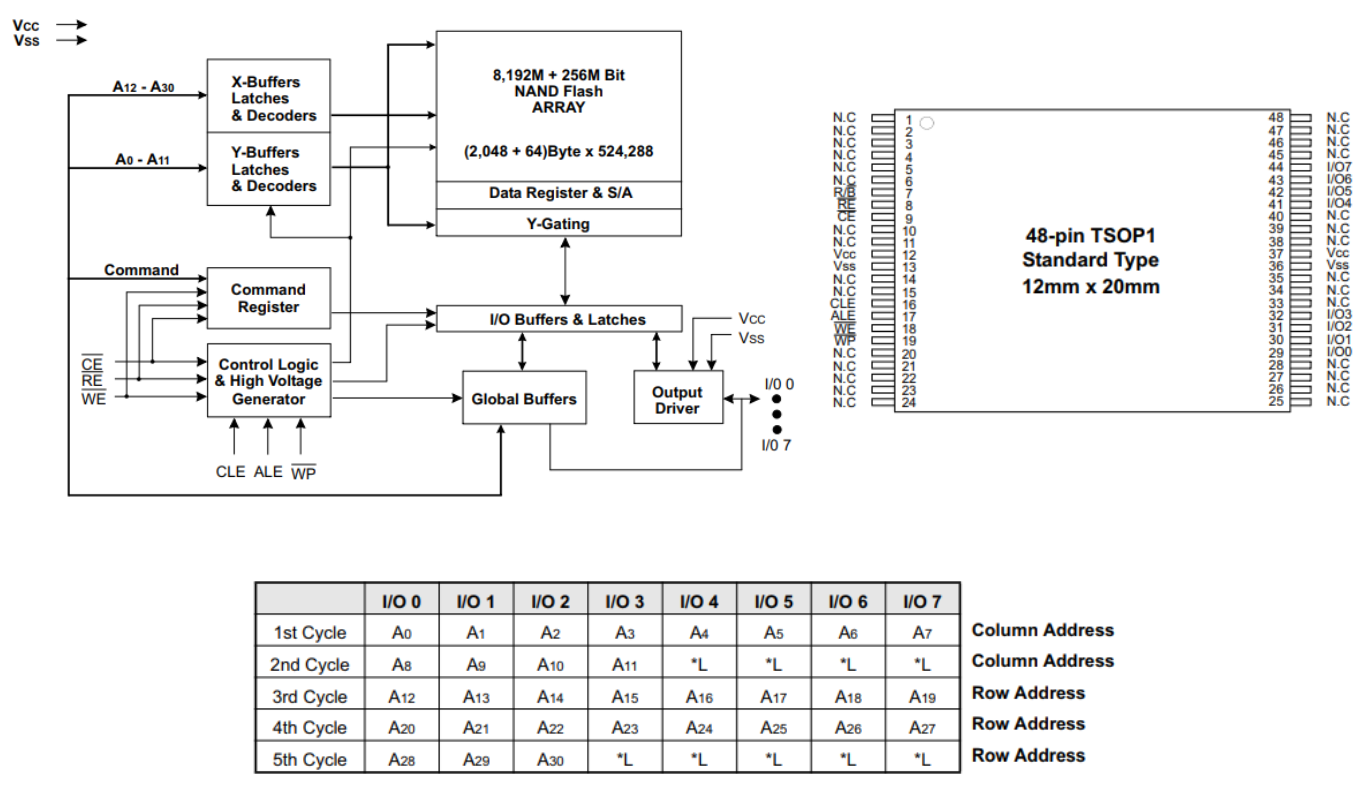

Parallel NAND Flash

블럭 다이어그램

Nand 플래시의 주소를 지정할 때에는 총 5번의 주소를 전송하여 지정할 수 있다.

- 2번은 Column 주소

- 3번은 Row 주소

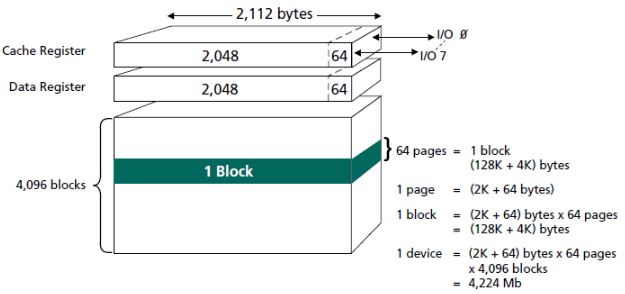

플래시의 용량 표기 시 8Gb라고 할 때 데이터를 8Gbit에 저장할 수 있고, ECC등의 정보를 담는 Spare 영역은 8Gbit에 포함되지 않고 별도의 영역을 가진다.

- 아래 Micron 8Gb 플래시도 별도의 256Mbit의 Spare 영역을 가지고 있다.

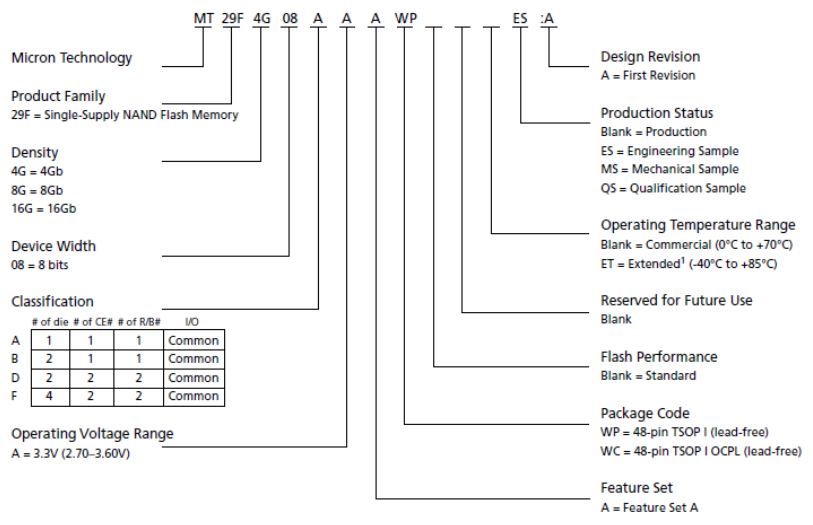

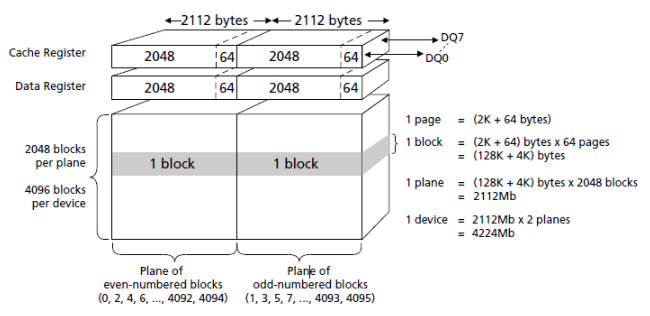

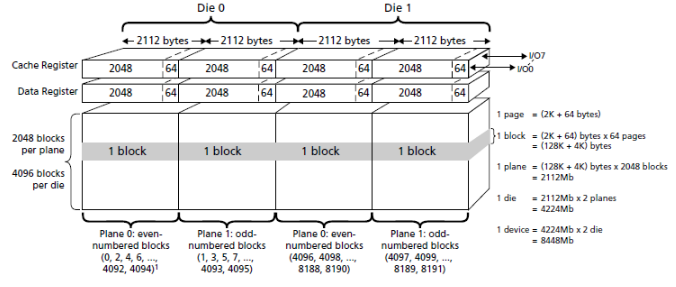

x8 vs x16

- 한 번에 8bit 또는 16bit 데이터 입출력을 전송할 수 있는 능력을 가진다. x8보다는 x16이 더 빠른 처리를 수행할 수 있다.

8Gb/x16 Micron NAND Flash (MT29F4G16BxB)

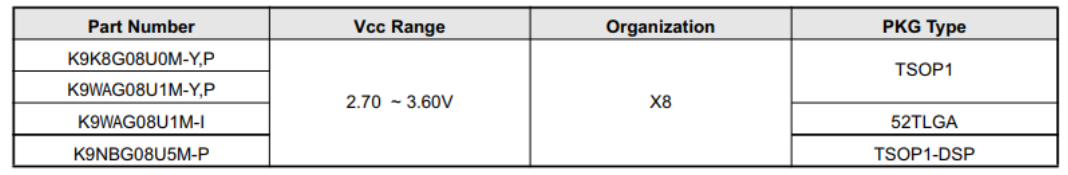

4Gb/x8 Samsung NAND Flash (K9K8G08U0M)

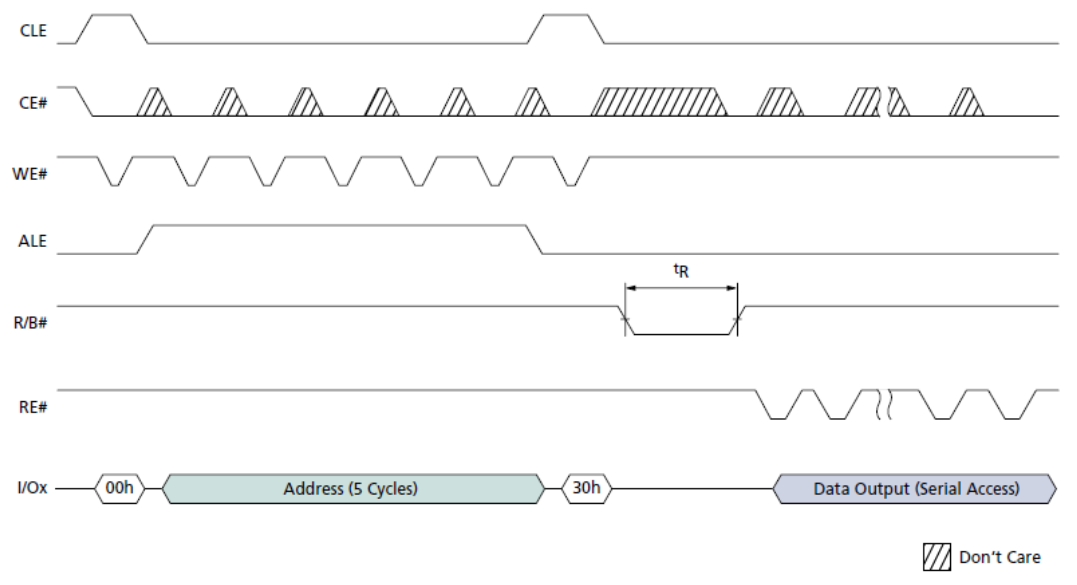

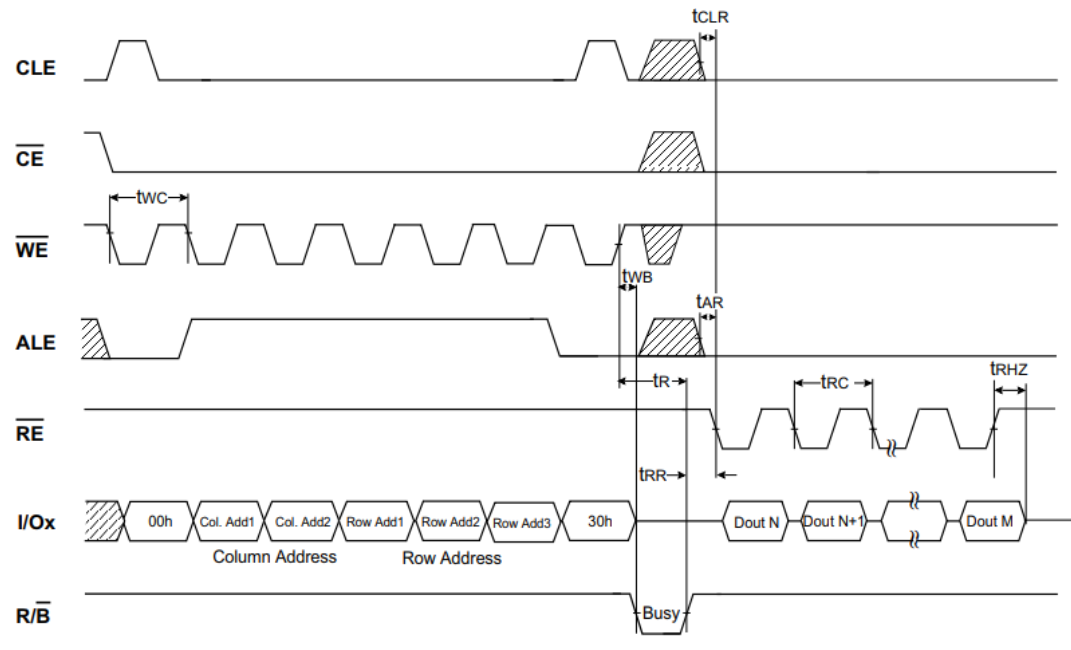

읽기 시그널

Micron(MT29F4G16BxB)

Samsung(K9K8G08U0M)

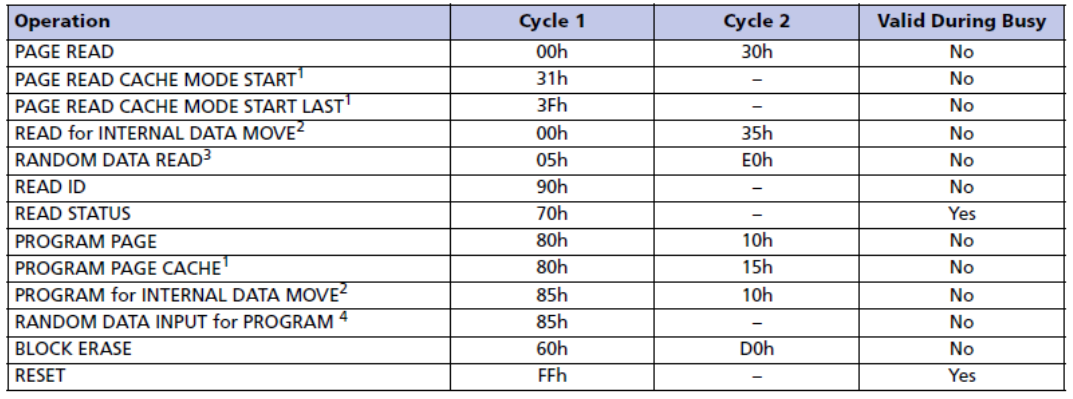

지원 명령

제조사 및 칩마다 지원 명령들이 다르다.

Micron(MT29F4G16BxB)

Samsung(K9K8G08U0M)

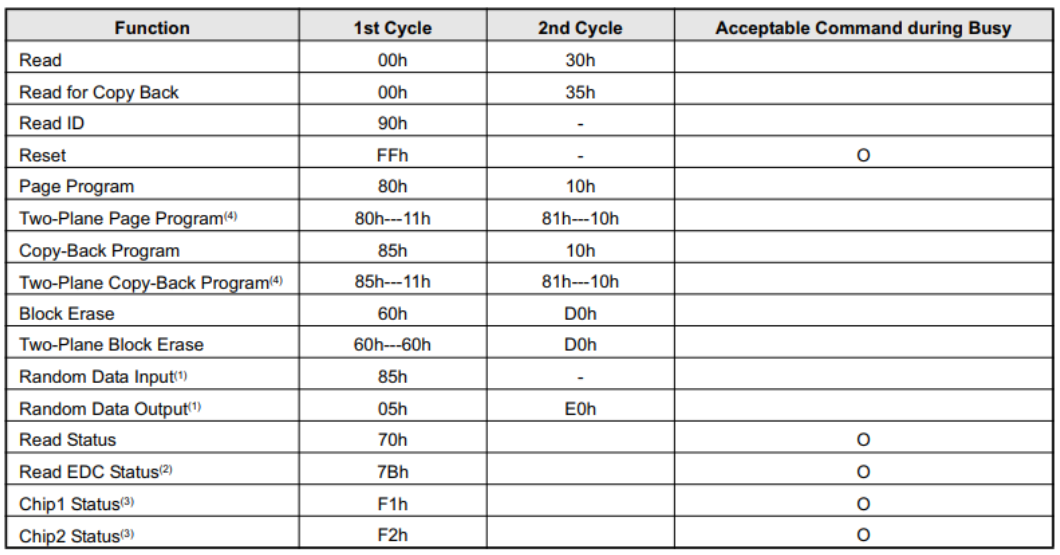

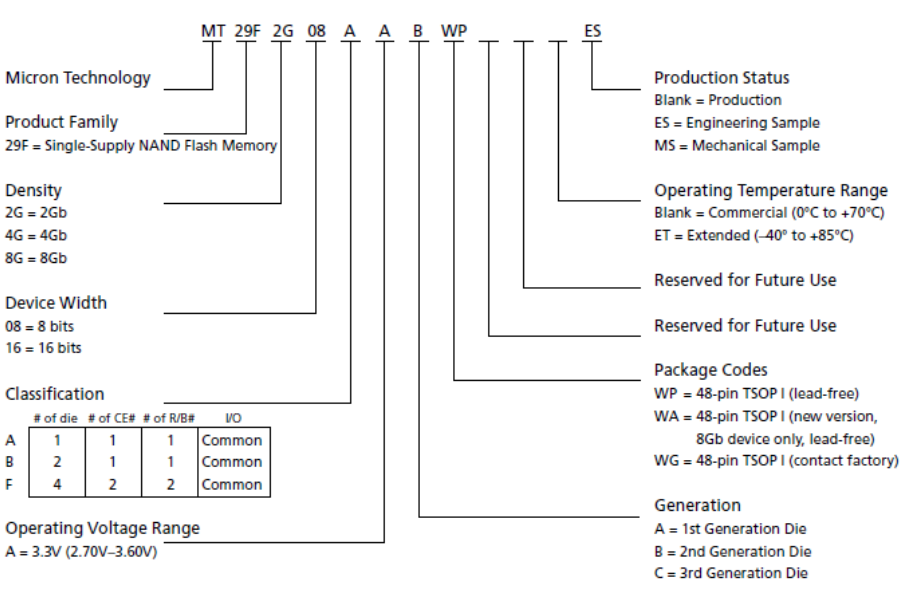

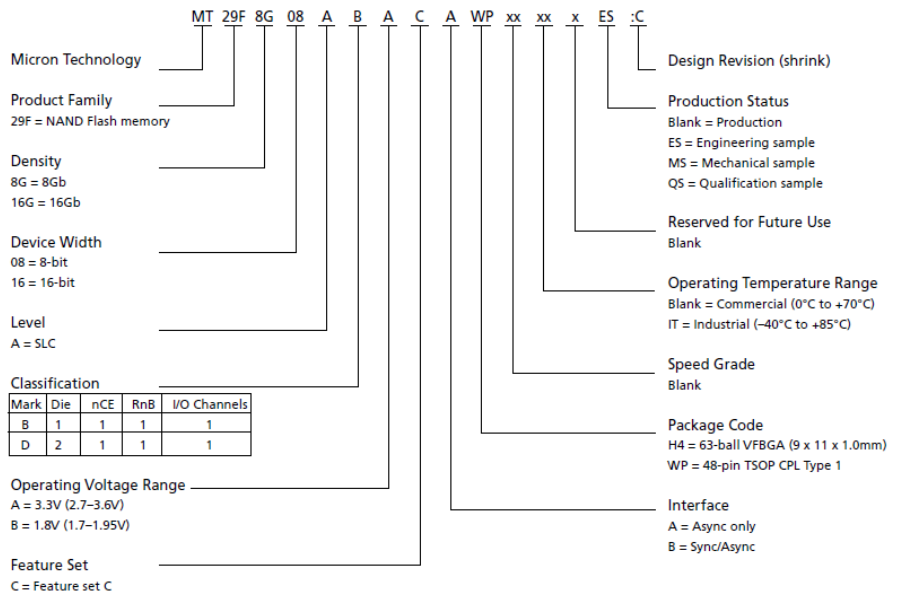

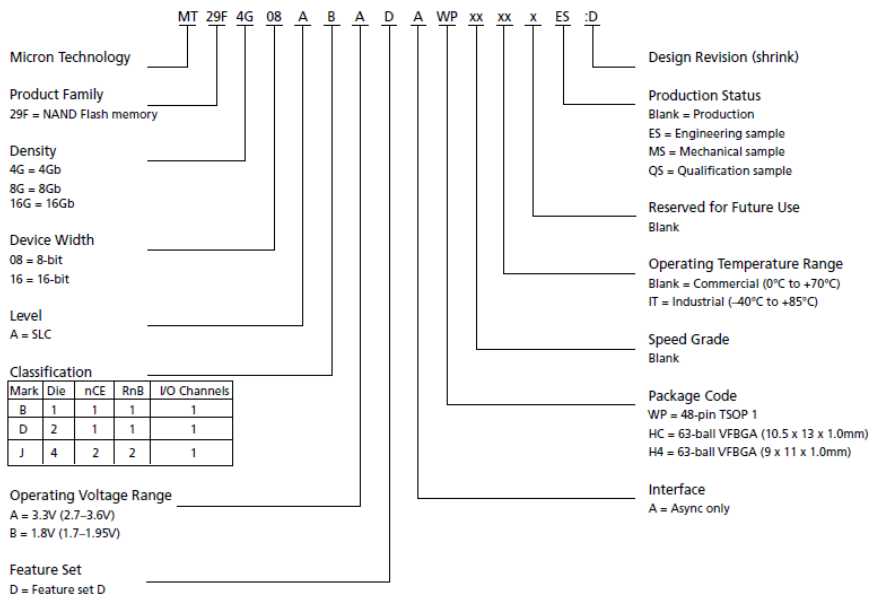

제품 코드 분류

주로 Micron SLC 1~4세대 제품들을 보여주고 있다.

- MLC 및 TLC NAND 들은 생략하였다.

Micron-SLC-1세대 (Feture Set A)

Micron-SLC-2세대 (Feture Set B)

Micron-SLC-3세대 (Feture Set C)

Micron-SLC-4세대 (Feture Set D)

Samsung(K9K8G08U0M)

블럭 및 페이지 사이즈

같은 회사의 동일한 용량이라도 generation에 따라 페이지 사이즈와 블럭수 및 OOB 사이즈 등이 다르다.

- 주로 Micron SLC 1~4세대 제품들을 보여주고 있다.

- MLC 및 TLC NAND 들은 생략하였다.

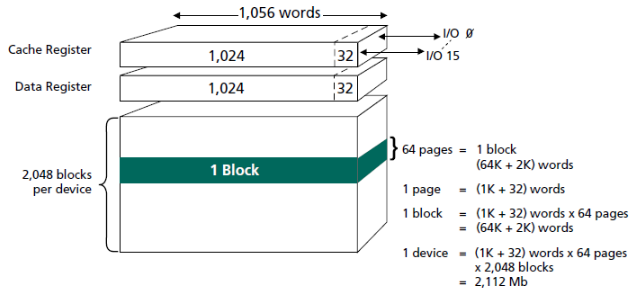

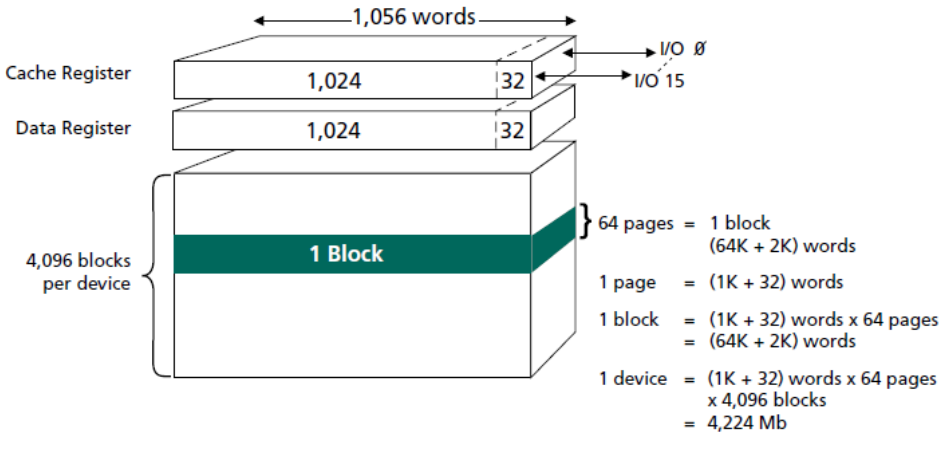

- 주의: 버스폭에 따라 사이즈(페이지 크기, OOB 사이즈) 값은 바이트(8bit)와 워드(16bit) 표기를 사용한다.

- x8: Bytes (8bits)

- x16: Words (16bits)

-

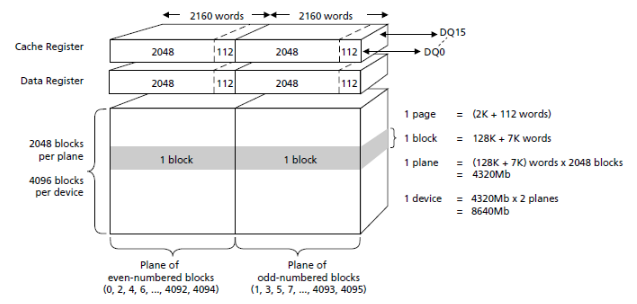

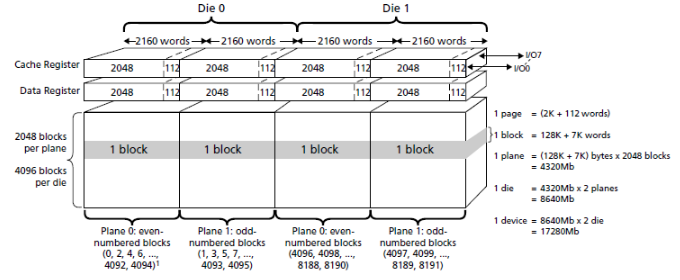

Plain

-

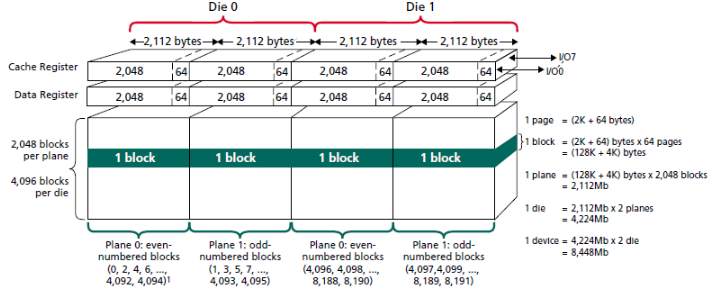

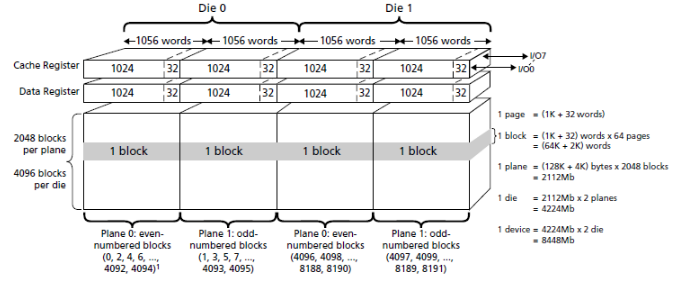

처리 속도를 높이기 위해 디바이스를 여러 개의 플레인으로 구성하여 사용한다.

-

Micron 1세대 SLC

MT29F4G08AAA & MT29F8G08DAA

- MT29F8G08DAA의 경우 두 개의 Chip Enable(CE#, CE2#)을 사용하여 4G x 2= 8G 용량을 사용할 수 있다.

MT29F8G08BAA & MT29F16G08FAA

- MT29F16G08FAA의 경우 두 개의 Chip Enable(CE#, CE2#)을 사용하여 8G x 2= 16G 용량을 사용할 수 있다.

Micron 2세대 SLC

MT29F2G08AxB

MT29F2G16AxB

MT29F4G08BxB & MT29F8G08FxB

- MT29F8G08FxB의 경우 두 개의 Chip Enable(CE#, CE2#)을 사용하여 4G x 2= 8G 용량을 사용할 수 있다.

Micron(MT29F4G16BxB)

Micron 3세대 SLC

MT29F8G8xxxC

MT29F8G16xxxC

MT29F16G08xxxC

MT29F16G16xxxC

Micron 4세대 SLC

MT29F4G08xxxD

MT29F4G16xxxD

MT29F8G08xxxD & MT29F16G08xxxD

- MT29F16G08xxxD의 경우 두 개의 Chip Enable(CE#, CE2#)을 사용하여 8G x 2= 16G 용량을 사용할 수 있다.

MT29F8G16xxxD

Samsung

Samsung(K9K8G08U0M)

주소 지정

각 사의 NAND 플래시마다 주소 지정방법이 조금씩 다르다.

Micron(MT29F4G08BxB)

첫 블럭만 살펴보면

- 첫 블럭 영역

- 0x0000_0000 ~ 0x0003_ffff (미사용 영역 포함: 256KB)

- 첫 블럭의 첫 페이지 영역

- 0x0000_0000 ~ 0x0000_0fff (미사용 영역 포함: 4KB)

- 첫 페이지 데이터 영역

- 0x0000_0000 ~ 0x0000_07ff (2KB)

- 첫 페이지 Spare 영역

- 0x0000_0800 ~ 0x0000_083f (64B)

Micron(MT29F4G16BxB)

첫 블럭만 살펴보면

- 첫 블럭 영역

- 0x0000_0000 ~ 0x0001_ffff (미사용 영역 포함: 128KB)

- 첫 블럭의 첫 페이지 영역

- 0x0000_0000 ~ 0x0000_07ff (미사용 영역 포함: 2KB)

- 첫 페이지 데이터 영역

- 0x0000_0000 ~ 0x0000_03ff (1KB)

- 첫 페이지 Spare 영역

- 0x0000_0400 ~ 0x0000_041f (32B)

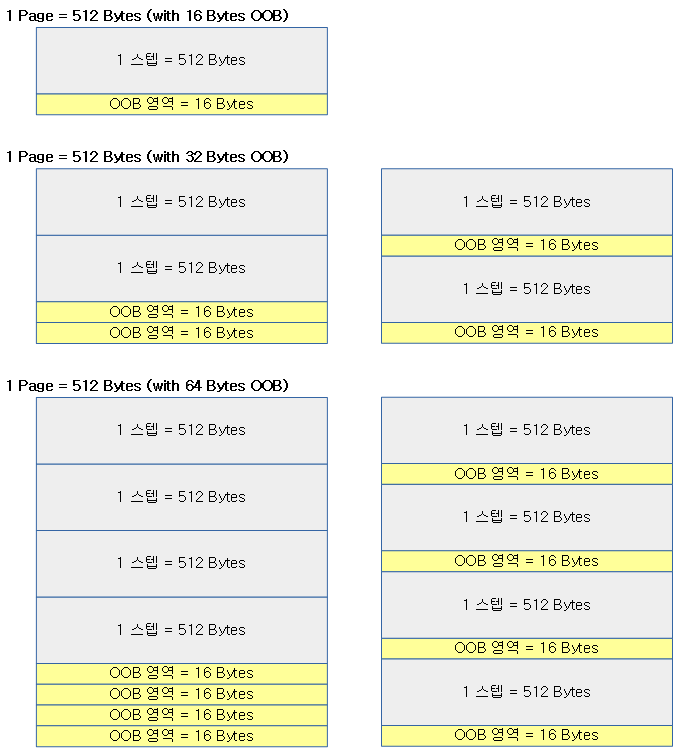

Spare Area 또는 OOB(Out Of Block)

NAND의 최소 단위는 페이지인데 1개의 페이지 크기는 칩 마다 다양한 크기를 갖는다.

- 512 바이트

- 1024 바이트

- 2048 바이트

- 4096 바이트

- 8192 바이트

- ….

ECC를 만들기 위해 사용되는 사이즈 범위를 스텝(Step)이라 하고 이 스텝의 사이즈는 다음과 같이 2 가지가 있다.

- 512 바이트

- 1024 바이트

매 데이터 페이지마다 Spare Area 또는 OOB(Out Of Block)이라고 불리는 추가 영역을 필요로한다. 이 곳에는 다음과 같은 정보가 담기며 각 제조사 NAND 플래시와 칩 마다 다르다.

- BI(Bad block Info) 또는 BBM(Bad Block Marker) 정보

- 1 바이트로 구성된다.

- 0xff인 경우 정상이고, 그 외의 값은 Bad Block을 의미한다.

- 2개가 있는 경우는 버스가 x16인 경우에 사용된다.

- ECC 정보

- 1 비트 Hamming의 경우 3바이트

- BCH-4의 경우 7바이트를 사용하며 OOB 내에서의 위치는 제조사 및 칩마다 다르다.

OOB 영역의 경우 1개의 페이지 뒤에 모여 있는 경우도 있고 1개 페이지 중간 스텝마다 위치하는 경우도 있다. OOB 영역의 크기는 다음과 같이 다양하다.

- 8, 16, 32, 64, 128, 218, 224, 400, 436, 448, 512, 640, 1024, 16764, 2048 bytes

- 16 * 4 스텝 = 64 bytes

- 16 * 8 스텝 = 128 bytes

- 28 * 4 스텝 = 112 bytes

- 28 * 8 스텝 = 224 bytes

- BBM(Bad Block Marker) 위치

- 보통 OOB(Out Of Block, Spare Area)의 첫 번째 바이트 또는 여섯 번째 위치

- ECC 알고리즘 종류

- Hamming

- NAND 플래시에 적용 시 512바이트당 최대 1비트 부호를 정정할 수 있다.

- 16바이트 단위로 일곱번째 바이트에 위치하고 3바이트 사용

- BCH-4

- NAND 플래시에 적용 시 512바이트당 최대 4비트 부호를 정정할 수 있다.

- 16바이트 단위로 열번째 바이트에 위치하고 7바이트 사용

- BCH-8

- NAND 플래시에 적용 시 512바이트당 최대 8비트 부호를 정정할 수 있다.

- 생략

- BCH-12

- NAND 플래시에 적용 시 512바이트당 최대 12비트 부호를 정정할 수 있다.

- 생략

- …

- Hamming

1 bit Hamming

Case 1) 16바이트 OOB – for 512B 페이지

- 0,0,0,0,0,B,E,E-E,0,0,0,0,0,0,0

Case 2) 64바이트 OOB – for 2KB 페이지

- B,B,0,0,0,0,E,E-E,0,0,0,0,0,0,0-0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0

- 0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0-0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0

- x16 버스를 사용하는 경우 워드(2 Byte) 단위로 처리되므로 첫 번째 워드의 각각의 바이트에 Bad Block 표기가 기재된다.

Case 3) 128바이트 OOB – for 4KB 페이지

- B,B,0,0,0,0,E,E-E,0,0,0,0,0,0,0-0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0

- 0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0-0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0

- 0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0-0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0

- 0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0-0,0,0,0,0,0,E,E-E,0,0,0,0,0,0,0

BCH-4

Case 1) 16바이트 OOB – for 512B 페이지

- 0,0,0,0,0,B,0,0-0,E,E,E,E,E,E,E

Case 2) 64 바이트 OOB – for 2KB 페이지

- B,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

Case 3) 128 바이트 OOB – for 4KB 페이지

- B,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

Case 4) 256 바이트 OOB – for 8KB 페이지

- B,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

- 0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E-0,0,0,0,0,0,0,0-0,E,E,E,E,E,E,E

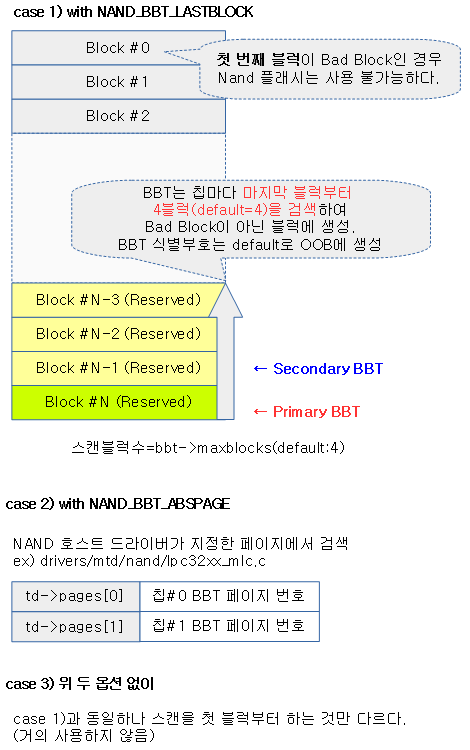

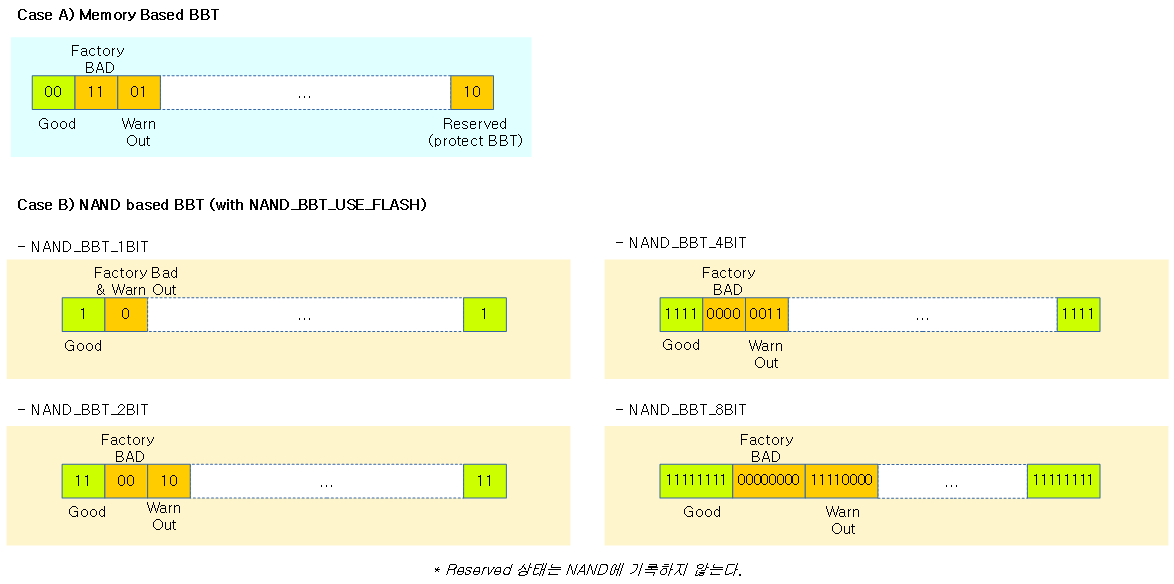

BBT(Bad Block Table)

두 개의 블럭을 사용하여 배드 블럭을 관리한다.

- 처음 부트로더가 Nand 전체를 Erase 한 후 마지막 블럭부터 검색하여 정상인 두 개의 블럭에 Primary 및 Secondary(Mirror) BBT 정보를 기록한다.

- BBT 블럭 내용에는 4개의 비트마다 하나의 블럭 정보를 담당하여 기록한다.

- 0x0000

- Factory Bad

- 커널에서는 2비트로 0x11

- 0x0001 ~ 0x1110

- Bad Block

- 0x1101: Reserved

- 커널에서는 2비트로 0x10

- 0x1110: Warn Out

- 커널에서는 2비트로 0x01

- 0x1111

- 정상(Good)

- 커널에서는 2비트로 0x00

- 0x0000

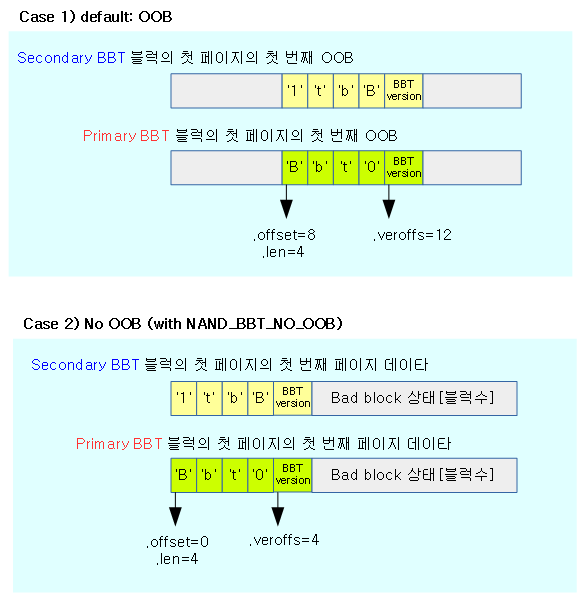

- BBT가 있는 블럭의 첫 페이지에 해당하는 OOB 영역에는 BBT 식별 부호가 담긴다.

- Primary BBT

- “Bbt0”

- Secondary BBT

- “1tbB”

- Primary BBT

- BBT에 Bad Block 정보 기록할 때

- 부트 로더에서 Nand Erase 시

- mtd-utils를 사용하여 수동으로 배드 블럭 마킹 시

- UBI를 사용하는 파티션의 경우 커널을 통해 Read/Write 에러 발생 시 자동으로

다음 그림은 BBT를 스캔하는 방법 3가지를 보여준다.

다음 그림은 BBT 식별부호가 저장되는 위치 2가지를 보여준다.

다음 그림은 커널에서 관리하는 BBT와 NAND에 위치한 BBT를 보여준다.

- 커널 BBT는 항상 사용되지만 NAND에서 BBT를 운영할지의 여부는 NAND_BBT_USE_FLASH 옵션의 사용 유무로 판단한다.

- NAND_BBT_CREATE 옵션

- BBT 가 없을 때 생성한다.

- NAND_BBT_WRITE 옵션

- NAND에 BBT 갱신을 가능하게 한다.

- NAND_BBT_CREATE 옵션

- NAND에 저장되는 Bad Block 상태값은 4가지 비트 타입 중 하나를 사용한다.

- 대부분 2비트를 사용한다. 일부는 8비트를 사용하는 경우도 있다.

- Reserved 상태는 커널 BBT에서만 관리하고 NAND에는 저장하지 않는다.

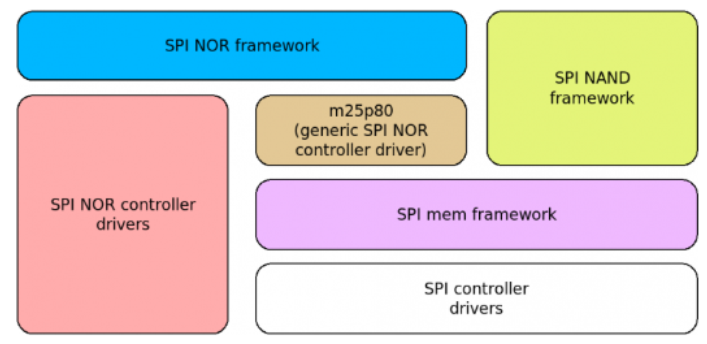

SPI를 위한 프레임워크

SPI-NOR 및 SPI-NAND를 위한 프레임워크도 준비되어 있다.

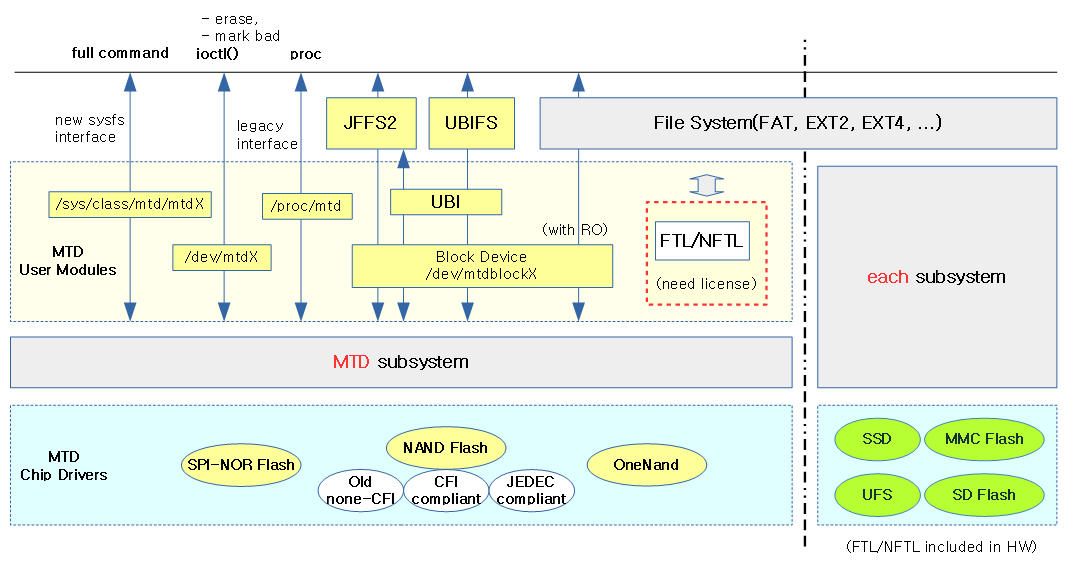

MTD & FTL Subsystem

MTD 서브시스템을 사용하는 인터페이스와 FTL/NFTL 서브시스템을 사용하는 분리하여 보여주고 있다.

- 리눅스 커널의 MTD subsystem에도 FTL 및 NFTL 코드가 있지만 라이센스 문제가 있어 상용 목적으로 사용할 수 없다.

- 보통 MTD 서브시스템의 FTL/NFTL을 사용하지 않고 대부분 제조사 컨트롤러 HW에 내장된 FTL을 사용한다.

MTD vs FTL

리눅스 커널에 FTL 및 NFTL 코드가 있고 소프트웨어만으로도 구현을 할 수는 있지만 라이센스 문제로 상용 목적으로 사용할 수는 없다

- 참고로 UBIFS의 경우 대부분의 FTL 기능을 담고 있다.

다음 MTD와 H/W로 구현된 FTL의 차이점을 간단히 알아본다.

- MTD

- 부트 로더 및 리눅스 커널이 배드 블럭 관리를 해야 한다.

- 부트 로더 및 리눅스 커널이 블럭별 레벨 관리를 해야 한다.

- 레벨 관리: 특정 블럭에 write가 집중되지 않게 한다.

- 부트 로더 및 리눅스 커널이 ECC 정보를 추가로 기록해야 한다.

- UBIFS를 사용하는 경우 FTL의 대부분 기능을 처리해준다.

- FTL

- 컨트롤러 H/W가 배드 블럭 관리를 자동으로한다.

- 일정 공간을 여분으로 두어 하드웨어가 배드 블럭 교체에 사용한다.

- 컨트롤러 H/W가 블럭별 레벨 관리를 자동으로 한다.

- 컨트롤러 H/W가 ECC 정보를 자동으로 기록하여 관리한다.

- 컨트롤러 H/W가 배드 블럭 관리를 자동으로한다.

FTL의 주요 기능

- Logical Block Mapping

- Wear Levelling

- Garbage Collection

- Write Amplification

Case A) NAND Flash

예를 들어 MTD 레이어를 사용하고, MTD chip 드라이버에 NAND Flash를 사용하는 경우는 다음과 같이 동작함을 알 수 있다.

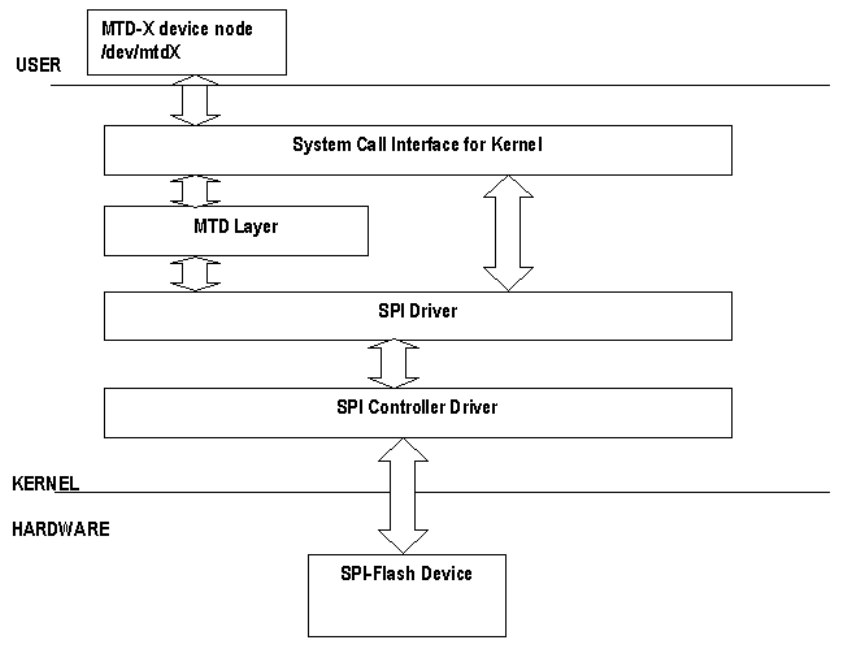

Case B) SPI Flash

예를 들어 MTD 레이어를 사용하고, MTD chip 드라이버에 SPI Flash를 사용하는 경우는 다음과 같이 동작함을 알 수 있다.

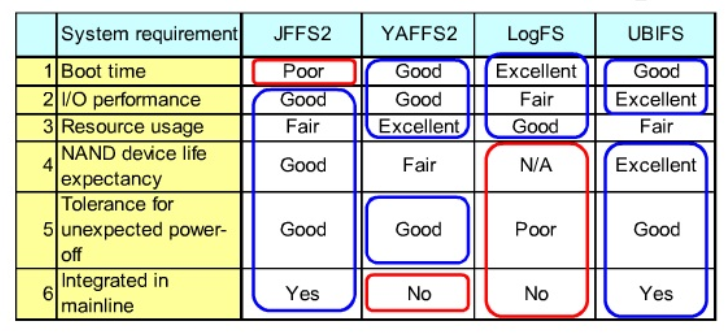

MTD를 사용하는 파일시스템간 비교

ECC(Error Checking & Correction)

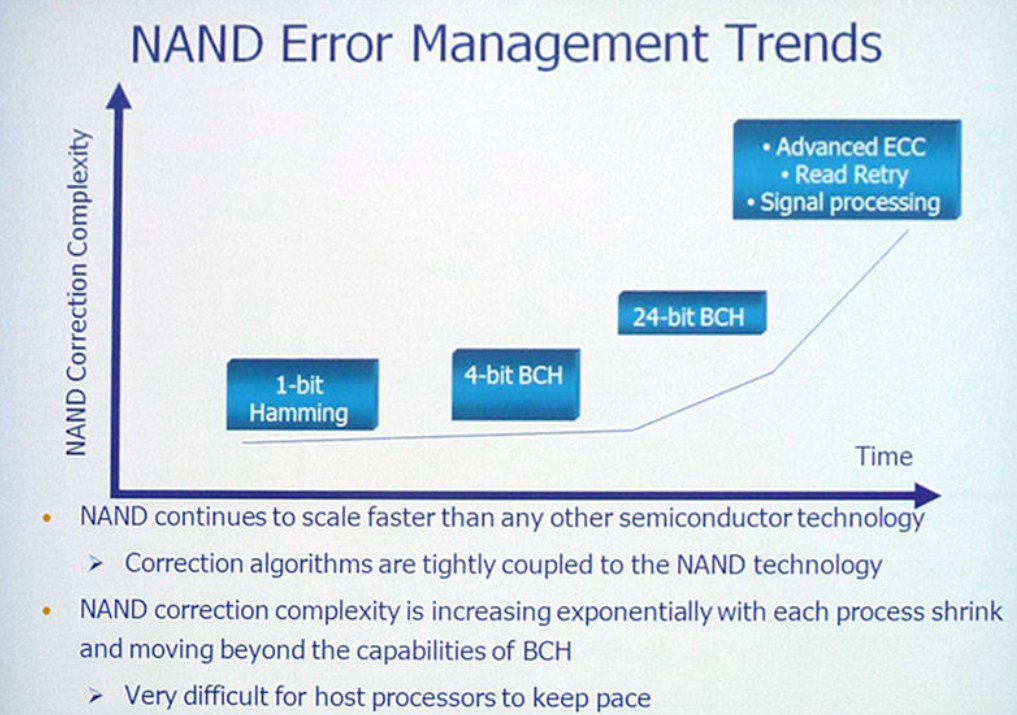

낸드에 에러율이 높으므로 이를 보완할 수 있도록 기본적으로 ECC를 사용한다. 칩 선폭이 큰 SLC 같은 경우 Hamming이나 BCH 알고리즘으로 충분하다. MLC나 TLC의 경우는 더욱 높은 수준의 ECC가 필요해졌다. 참고로 1 비트 Hamming은 한 스텝(512 또는 1024 바이트) 당 에러 정정 비트는 1비트만 가능하다. 즉 한 스텝에서 동시에 2개 비트가 에러가 발생하는 경우 교정하지 못한다. 더 높은 수준의 ECC를 위해 BCH-4, BCH-8, BCH-12, … 등을 사용하는데 BCH 뒤에 붙는 숫자는 보정 가능한 비트 수를 의미한다.

1 bit Hamming

다음은 가장 간단한 ECC 알고리즘 중 하나인 Hamming으로 한 스텝(512 또는 1024 바이트) 데이터를 위해 필요한 ECC 비트를 산출하였다.

- X축에 필요한 ECC=6bits

- Y축에 필요한 ECC=18bits

- 총 24bits(3 bytes)

다음 그림은 512바이트(x8) 데이터의 hamming 알고리즘을 사용하여 ECC를 만드는 방법을 보여준다.

- X(column)축의 첫 번째 ECC 비트를 만드는 방법은 다음과 같다.

- 0x000 ~ 0x1ff의 bit7..bit4를 모두 Exclusive OR한 값

- Y(row)축의 첫 번째 ECC 비트를 만드는 방법은 다음과 같다.

- 0x000 ~ 0x0ff의 bit7..bit0을 모두 Exclusive OR한 값

NAND 셀(SLC, MLC, TLC)

NAND 플래시에서 1 셀당 저장할 수 있는 비트가 다음과 같다.

- SLC

- 1 셀당 1비트

- 블럭당 약 100,000회 erase 가능

- 고가

- MLC

- 1셀당 2비트

- 블럭당 약 10,000회 erase 가능

- 중간

- TLC

- 1셀당 3비트

- 블럭당 약 1,000회 erase 가능

- 저가

SLC에 비해 MLC 및 TLC의 경우 에러 메니지먼트가 더욱 중요해서 더 복잡한 ECC를 채용하였음을 보여준다.

NAND Error Management Trends

NAND 플래시에서 점점 진보된 ECC 알고리즘으로 변화되고 있는 트렌드를 보여준다.

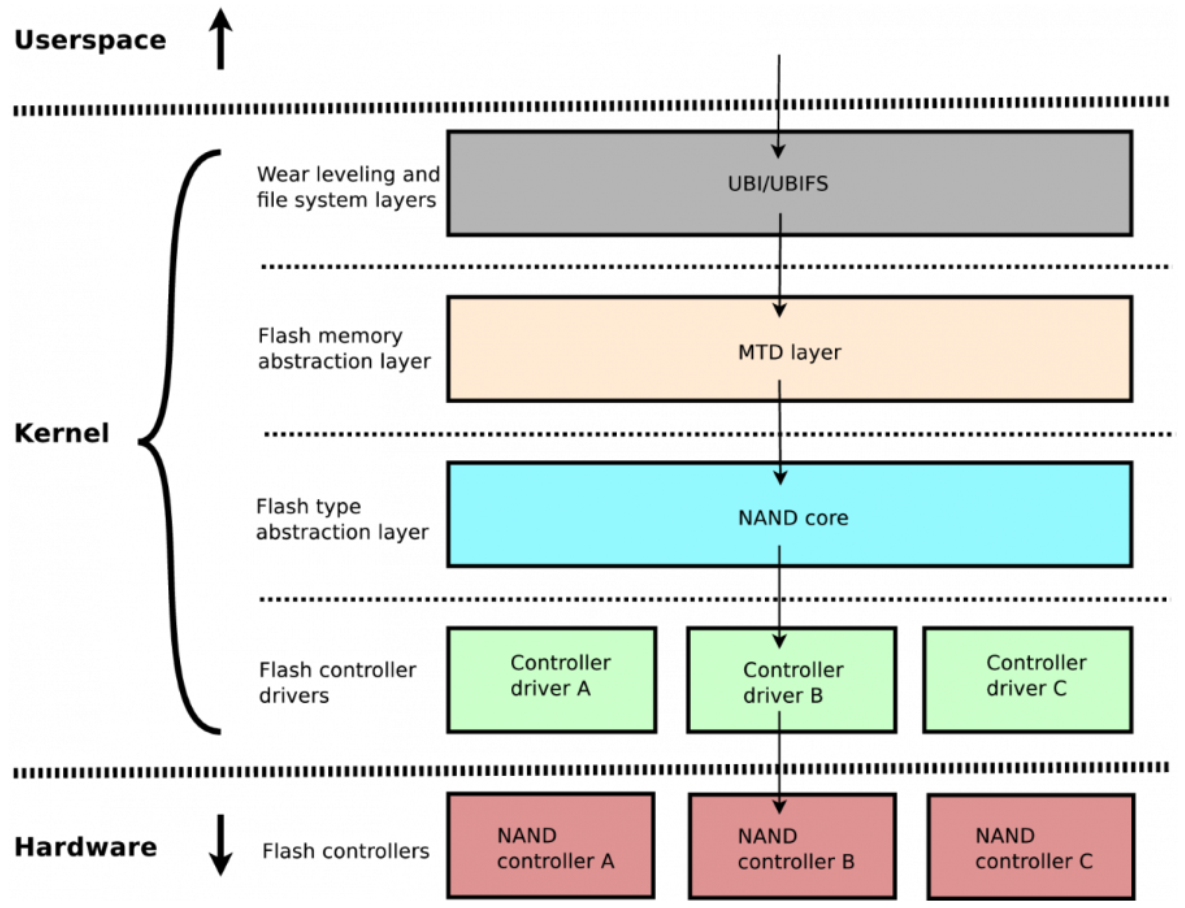

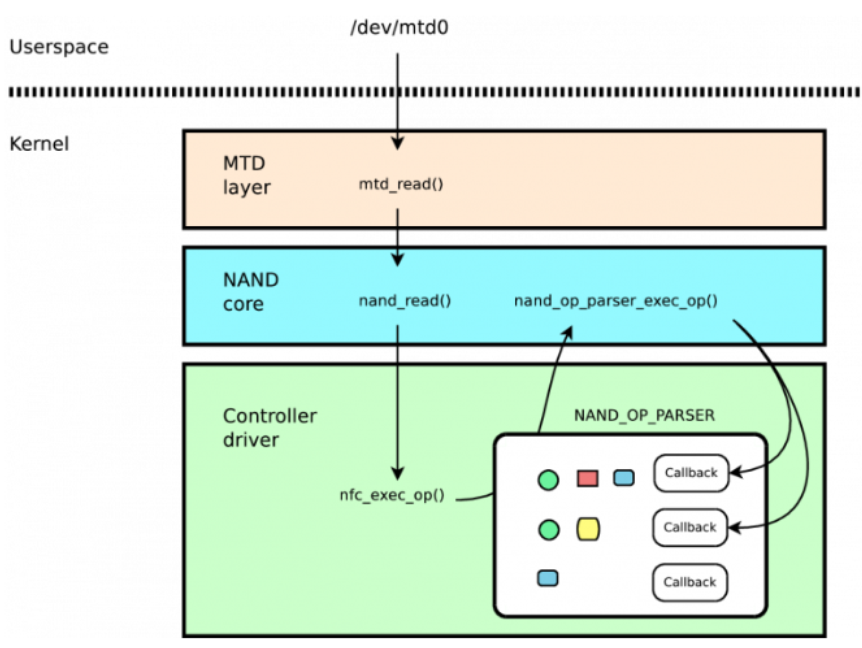

MTD Subsystem

MTD 오퍼레이션 명령 단위

플래시 메모리를 읽기 위해 다음과 같이 동작한다.

- 명령(Cmd) 전송 –> 주소들 전송 –> 명령(Cmd) 전송 –> 대기 –> 데이터 수신

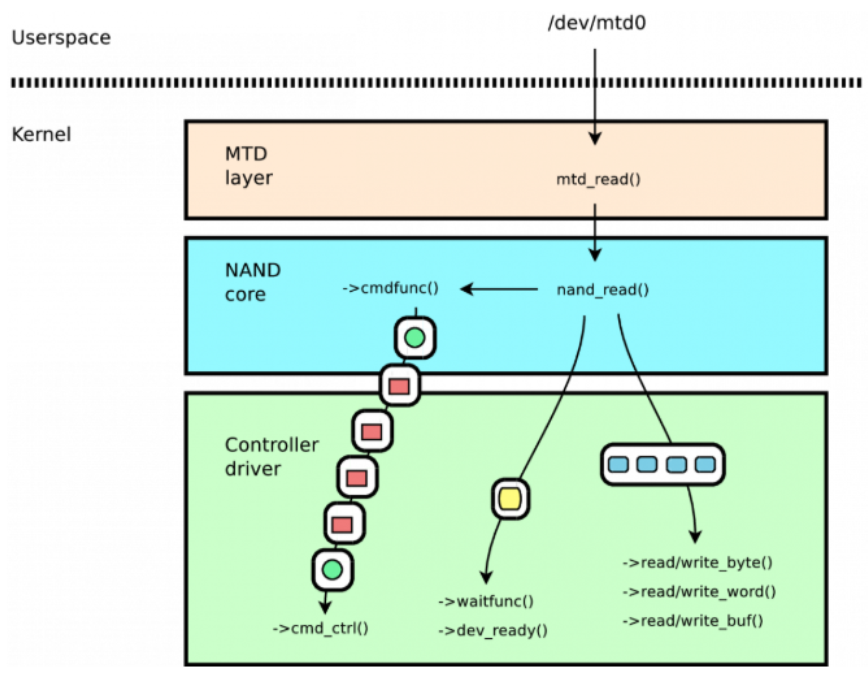

기존 커널 오퍼레이션

NAND 컨트롤러 드라이버 구현 시 nand를 읽기 위해 여러 개의 operation을 구현해야 했다.

바뀐 새 커널(v4.16) 오퍼레이션

변경된 커널 v4.16에서는 NAND 컨트롤러 드라이버 구현 시 nand를 읽기 위해 단순화된 operation을 구현하면 된다. 당분간 기존 operation도 호환 목적으로 같이 병행하여 사용한다.

- (*exec_op)

- 추가된 후크 함수로 다음 명령들을 대체한다.

- ->cmdfunc()

- ->{read,write}_{buf,byte,word}()

- ->dev_ready()

- ->waifunc()

- 추가된 후크 함수로 다음 명령들을 대체한다.

참고

- MTD(Memory Technology Device) -1- | 현재 글

- MTD(Memory Technology Device) -2-

- MTD(Memory Technology Device) -3-

- General MTD documentation | MTD

- Nand 관련 | Bootlin

- Bootlin contributes a new interface to the Linux NAND subsystem | Bootlin

- Bootlin adds SPI NAND support to U-Boot | Bootlin

- Flash filesystems | Free Electrons(Bootlin)

- Modernizing the NAND framework: The Big Picture | Free Electrons(Bootlin) – 다운로드 pdf

- NAND FLASH이 구조와 특징 | noority

- JFFS2, UBIFS, and the growth of flash storage | LWN.net

- NAND플래시 메모리의 신뢰성을 유지하는 기술 | Gigglehd.com

- Introduction to Nand Memories | RidgeRun

- 개발자를 위한 SSD (Coding for SSD) | 이성욱

- Nand Flash 다루기 | 삶의길

- FTL(flash translation layer) 관련 자료 1 | 삶의길

- ONFI(Open Nand Flash Interface) Specification | ONFI

- Understanding the Flash Translation Layer (FTL) Specification | Intel – 다운로드 pdf

- Linux에서 Nand-FTL 기술의 사용 | Appkr.memo

- 짱가의 SD카드 강좌 #1 : SD카드에 대한 기초 지식(Background) | 아웃라이어

- An Introduction to SPI-NOR Subsystem | TI – 다운로드 pdf

- 삼성 NAND Flash ECC 알고리즘 해부하기 (1) | 지정웅

- 삼성 NAND Flash ECC 알고리즘 해부하기 (2) | 지정웅

UBIFS 의 경우, mtdblock 이 없어도 가능한 것으로 알고 있습니다.

JFFS2 나 YAFFS2 는 필요하구요.

https://bootlin.com/blog/managing-flash-storage-with-linux/

안녕하세요?

소중한 정보 감사드립니다. UBIFS 관련해서는 먼저 수정하였습니다.

mtdblock과 관련하여 그림 변경을 고민해보겠습니다.

감사합니다.