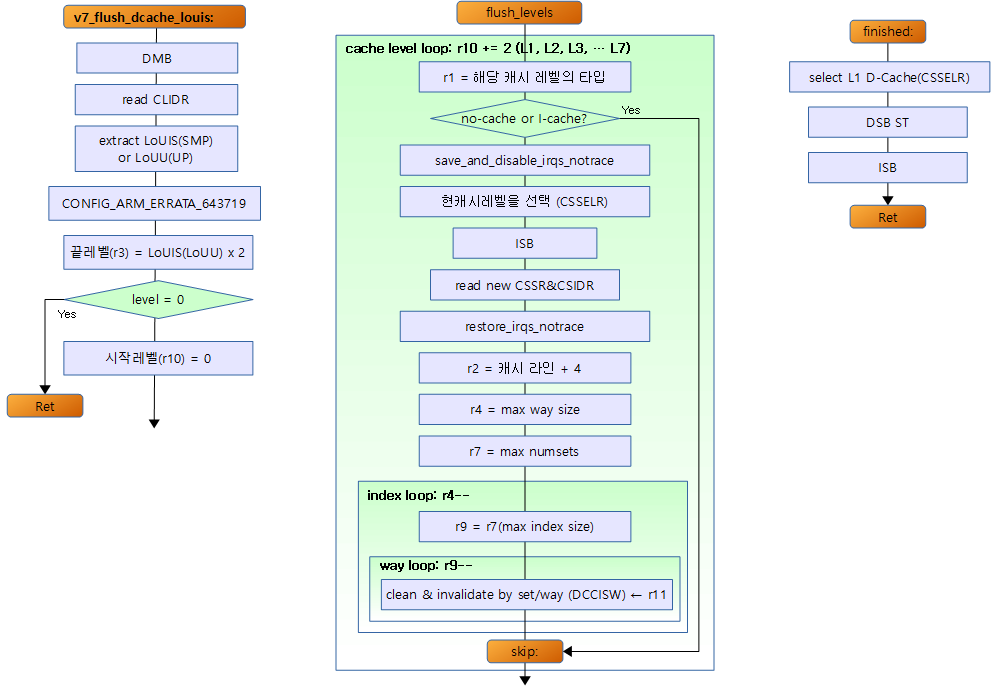

- compressed/head.S 에서 사용하였던 __armv7_mmu_cache_flush: 루틴과 거의 동일하다.

- 데이터 캐시를 지우라고 요청하면 SoC 정보를 확인하여 지원하는 최종 캐시레벨을 확인한 후 L1 부터 해당 캐시 레벨까지 flush한다.

- 해당 캐시 레벨에서는 index와 way를 사용하여 하나씩 삭제한다.

hierarchical cache

- ARMv6 아키텍처까지는 ARM 아키텍처에서 L1 캐시만 지원하였었다.

- ARMv7 아키텍처부터 다단계의 캐시를 지원하게되었다.

- 다단계 캐시, ARM에서는 hierarchical cache 구조 라고 한다.

v7_flush_dcache_louis()

arch/arm/mm/cache-v7.S

/*

* v7_flush_dcache_louis()

*

* Flush the D-cache up to the Level of Unification Inner Shareable

*

* Corrupted registers: r0-r7, r9-r11 (r6 only in Thumb mode)

*/

ENTRY(v7_flush_dcache_louis)

dmb @ ensure ordering with previous memory accesses

mrc p15, 1, r0, c0, c0, 1 @ read clidr, r0 = clidr

ALT_SMP(ands r3, r0, #(7 << 21)) @ extract LoUIS from clidr

ALT_UP(ands r3, r0, #(7 << 27)) @ extract LoUU from clidr

#ifdef CONFIG_ARM_ERRATA_643719

ALT_SMP(mrceq p15, 0, r2, c0, c0, 0) @ read main ID register

ALT_UP(reteq lr) @ LoUU is zero, so nothing to do

ldreq r1, =0x410fc090 @ ID of ARM Cortex A9 r0p?

biceq r2, r2, #0x0000000f @ clear minor revision number

teqeq r2, r1 @ test for errata affected core and if so...

orreqs r3, #(1 << 21) @ fix LoUIS value (and set flags state to 'ne')

#endif

ALT_SMP(mov r3, r3, lsr #20) @ r3 = LoUIS * 2

ALT_UP(mov r3, r3, lsr #26) @ r3 = LoUU * 2

reteq lr @ return if level == 0

mov r10, #0 @ r10 (starting level) = 0

b flush_levels @ start flushing cache levels

ENDPROC(v7_flush_dcache_louis)

- mrc p15, 1, r0, c0, c0, 1

- LoUU/LoUIS를 추출하기 위해 CLIDR을 읽어온다.

- ALT_SMP(ands r3, r0, #(7 << 21))

- SMP 시스템에서 CLIDR의 LoUIS 필드를 추출해온다.

- ERRATA_643719

- 특정 프로세서의 CLIDR.LOUIS가 잘못 기록이 되어 있어서 이를 보정해주는 코드

- Cortex-A9 r1p0 이전 버전에서 LoUIS 값이 1이 아닌 0으로 기록된 것을 잡아준다.

- ALT_SMP(mov r3, r3, lsr #20)

- r3: 읽어온 값을 우측으로 쉬프트하여 LoUIS x 2와 같은 값으로 만든다.

- d-cache를 어느 캐시 레벨까지 flush할지 결정하기 위함.

- r3: 읽어온 값을 우측으로 쉬프트하여 LoUIS x 2와 같은 값으로 만든다.

- reteq lr

- 읽어온 LoUIS가 0이면 d-cache의 flush를 포기하고 루틴을 빠져나간다.

- mov r10, #0

- 시작 캐시 레벨을 0(L1)부터 준비한다.

- b flush_levels

- v7_flush_dcache_all() 루틴 중간에 있는 flush_levels 레이블을 같이 사용한다.

v7_flush_dcache_all()

/*

* v7_flush_dcache_all()

*

* Flush the whole D-cache.

*

* Corrupted registers: r0-r7, r9-r11 (r6 only in Thumb mode)

*

* - mm - mm_struct describing address space

*/

ENTRY(v7_flush_dcache_all)

dmb @ ensure ordering with previous memory accesses

mrc p15, 1, r0, c0, c0, 1 @ read clidr

ands r3, r0, #0x7000000 @ extract loc from clidr

mov r3, r3, lsr #23 @ left align loc bit field

beq finished @ if loc is 0, then no need to clean

mov r10, #0 @ start clean at cache level 0

flush_levels:

add r2, r10, r10, lsr #1 @ work out 3x current cache level

mov r1, r0, lsr r2 @ extract cache type bits from clidr

and r1, r1, #7 @ mask of the bits for current cache only

cmp r1, #2 @ see what cache we have at this level

blt skip @ skip if no cache, or just i-cache

#ifdef CONFIG_PREEMPT

save_and_disable_irqs_notrace r9 @ make cssr&csidr read atomic

#endif

mcr p15, 2, r10, c0, c0, 0 @ select current cache level in cssr

isb @ isb to sych the new cssr&csidr

mrc p15, 1, r1, c0, c0, 0 @ read the new csidr

#ifdef CONFIG_PREEMPT

restore_irqs_notrace r9

#endif

and r2, r1, #7 @ extract the length of the cache lines

add r2, r2, #4 @ add 4 (line length offset)

ldr r4, =0x3ff

ands r4, r4, r1, lsr #3 @ find maximum number on the way size

clz r5, r4 @ find bit position of way size increment

ldr r7, =0x7fff

ands r7, r7, r1, lsr #13 @ extract max number of the index size

loop1:

mov r9, r7 @ create working copy of max index

loop2:

ARM( orr r11, r10, r4, lsl r5 ) @ factor way and cache number into r11

THUMB( lsl r6, r4, r5 )

THUMB( orr r11, r10, r6 ) @ factor way and cache number into r11

ARM( orr r11, r11, r9, lsl r2 ) @ factor index number into r11

THUMB( lsl r6, r9, r2 )

THUMB( orr r11, r11, r6 ) @ factor index number into r11

mcr p15, 0, r11, c7, c14, 2 @ clean & invalidate by set/way

subs r9, r9, #1 @ decrement the index

bge loop2

subs r4, r4, #1 @ decrement the way

bge loop1

skip:

add r10, r10, #2 @ increment cache number

cmp r3, r10

bgt flush_levels

finished:

mov r10, #0 @ swith back to cache level 0

mcr p15, 2, r10, c0, c0, 0 @ select current cache level in cssr

dsb st

isb

ret lr

ENDPROC(v7_flush_dcache_all)

- decompressed/head.S에서 d-cache를 flush한 로직과 거의 흡사하다.

- way와 index 루프 순서만 기존과 바뀌었다.