<ARMv8.x>

ARM64 시스템 주요 레지스터

캐시

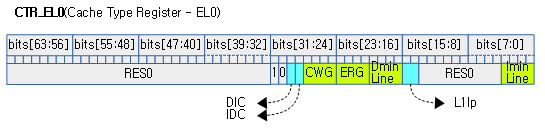

CTR_EL0(Cache Type Register – EL0)

캐시 타입을 알아오는 레지스터이다.

- 참고: CTR_EL0, Cache Type Register | ARM

- DIC

- Instruction cache invalidation requirements for instruction to data coherence

- 0=PoU를 위해 명령 캐시의 invalidation이 필요하다.

- 1=PoU를 위해 명령 캐시의 invalidation이 필요하지 않다.

- IDC

- Data cache clean requirements for instruction to data coherence

- 0=PoU를 위해 데이터 캐시의 clean이 필요하다. 단 다음 조건 제외

- CLIDR_EL1.LoC == 0 or (CLIDR_EL1.LoUIS == 0 && CLIDR_EL1.LoUU == 0)

- 1=PoU를 위해 데이터 캐시의 clean이 필요하지 않다.

- CWG(Cache Writeback Granule)

- 0~1=CWG 정보를 제공하지 않는다.

- 2~9=Cache Writeback Granule로 2^n 워드를 초과하지 않는다.

- 10 이상=reserved

- ERG(Exclusives Reservation Granule)

- 0=ERG 정보를 제공하지 않는다.

- 1~9=Exclusives Reservation Granule로 2^n 워드를 초과하지 않는다.

- 10 이상=reserved

- DminLine

- 데이터 캐시 라인 사이즈로 2^n 워드

- L1Ip

- 레벨 1 명령 캐시 정책

- 0=VPIPT (ARMv8.2 이상에서 가능)

- 1=AIVIVT

- 2=VIPT

- 3=PIPT

- 레벨 1 명령 캐시 정책

- IminLine

- 명령 캐시 라인 사이즈로 2^n 워드

예) Cortex-A72, CTR_EL0=0x8444_c004

- DIC=0

- IDC=0

- CWG=4(16 words)

- ERG=4(16 words)

- DminLine=4(16 words)

- L1Ip=3(PIPT)

- IminLine=4(16 words)

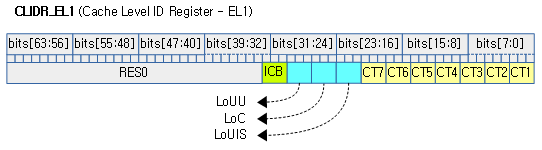

CLIDR_EL1(Cache Level ID Register – EL1)

구성된 레벨별 캐시 타입(명령 only, 데이터 only, 명령+데이터 분리, 명령+데이터 통합)을 구분하고 최상위 통합 캐시 레벨과 최상위 캐시 일관성 레벨을 알려주는 레지스터이다.

- 참고: CLIDR_EL1, Cache Level ID Register | ARM

- ICB(Inner Cache Boundary)

- Inner 캐시 영역

- 예) ICB=2

- L2 캐시까지 Inner 캐시 영역이다.

- LoUU(Level of Unification Uniprocessor)

- Uni 프로세서 시스템에서 최상위 통합 캐시 레벨

- Uni 프로세서 시스템에서 PoU 개념과 동일하다.

- LoC(Level of Coherece)

- 최상위 캐시 일관성 레벨

- PoC 개념과 동일하다.

- LoUIS(Level of Inner Shareable)

- Inner 공유 영역내의 코어에서 최상위 통합 캐시 레벨

- SMP 시스템에서 PoU 개념과 동일하다.

- CType1 ~ CType7

- 캐시 레벨 별 캐시 타입

- 0=no cache

- 1=명령 캐시만 존재

- 2=데이터 캐시만 존재

- 3=명령 캐시와 데이터 캐시 분리

- 4=명령 캐시와 데이터 통합 캐시

- 캐시 레벨 별 캐시 타입

예) Cortex-A72, CIDR_EL1=0xa20_0023

- ICB=0

- LoUU=2(L2 레벨)

- LoC=2(L2 레벨)

- LoUIS=2(L2 레벨)

- CT7 ~ CT3=0(L7 ~ L3 캐시 없음)

- CT2=4(L2 캐시가 통합 캐시)

- CT1=3(L1 캐시가 분리 캐시)

프로세스

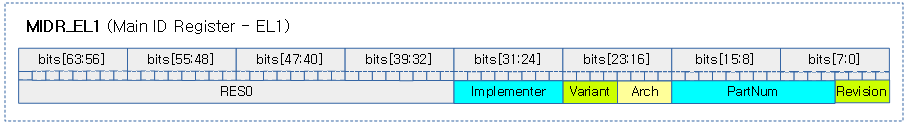

MIDR_EL2 (Main ID Register – EL2)

메인 ID를 담은 레지스터이다.

- 참고: MPIDR_EL1, Main ID Register | ARM

- Implementer

- 설계자 코드(ARM, Broadcom, Cavium, DEC, …)

- Variant

- variant 번호

- Architecture

- ARM 아키텍처 코드

- PartNum

- 파트 번호

- Revision

- 리비전 번호

MPIDR_EL2 (Multiprocessor Affinity Register – EL2)

Multiprocessor affinity 레벨을 담은 레지스터이다.

- AFF3

- Affinity level 3

- U

- Uniprocess 시스템 여부를 나타낸다.

- 0=SMP

- 1=UP

- MT

- 로지컬 PE의 최소 affinity 레벨 .

- 0=affinity 0이 최대 독립적

- 1=affinity 0이 매우 밀착 (Multi-Thread)

- AFF2

- Affinity level 2

- AFF1

- Affinity level 1

- AFF0

- Affinity level 0

CPU Feature 식별

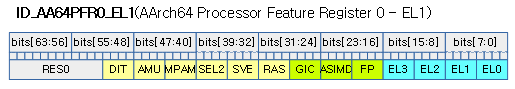

ID_AA64PFR0_EL1(AArch64 Processor Feature Register 0 – EL1)

AArch64 상태에 구현된 프로세서 feature를 알아오는 레지스터 0번이다.

- DIT(Data Independent Timing)

- 0=어떠한 명령도 constant 실행 시간을 보장하지 않는다.

- 1=명령의 constant 실행 시간을 보장한다.

- AMU(Activity Monitors Extension)

- 0=Activity Monitor 미구현

- 1=Activity Monitors Extension 버전 1 구현

- MPAM

- 0=MPAM Extension 미구현

- 1=MPAM Extension 구현

- SEL(Secure EL2)

- 0=Secure EL2 미구현

- 1=Secure EL2 미구현

- SVE(Scalable Vector Extension)

- 0=SVE 미구현

- 1=SVE 구현

- RAS

- 0=RAS Extension 미구현

- 1=RAS Extension 구현

- 2=ARMv8.4-RAS 구현

- GIC

- 0=GIC를 위한 System 레지스터 인터페이스 미구현

- 1=GIC를 위한 System 레지스터 인터페이스 구현

- ASIMD(Advanced SIMD)

- 0=Advanced SIMD 구현

- 1=Advanced SIMD 구현 + half-precision 실수 연산 추가

- 0xf=Advanced SIMD 미구현

- FP(Floating Point)

- 0=FP 구현

- 1=FP 구현 + half-precision 실수 연산 추가

- 0xf=FP 미구현

- EL3(Exception Level 3)

- 0=EL3 미구현

- 1=AArch64 에서만 EL3 구현

- 2=AArch32 및 AArch64 양쪽에서 EL3 구현

- EL2(Exception Level 2)

- 0=EL2 미구현

- 1=AArch64 에서만 EL2 구현

- 2=AArch32 및 AArch64 양쪽에서 EL2 구현

- EL2(Exception Level 2)

- 1=AArch64 에서만 EL1 구현

- 2=AArch32 및 AArch64 양쪽에서 EL1 구현

- EL0(Exception Level 0)

- 1=AArch64 에서만 EL0 구현

- 2=AArch32 및 AArch64 양쪽에서 EL0 구현

메모리 모델 기능

ID_AA64MMFR0_EL1 (Memory Model Feature Register 0 – EL1)

AArch64 상태에서 지원되는 메모리 모델을 알아오는 레지스터 0 이다.

- TGran4

- 4K 페이지 변환 지원 여부

- 0b0000=지원, 0b1111=미지원

- TGran64

- 64K 페이지 변환 지원 여부

- 0b0000=지원, 0b1111=미지원

- TGran16

- 16K 페이지 변환 지원 여부

- 0b0000=미지원, 0b0001=지원

- BigEndEL0

- EL0에서 Mixed 엔디안 지원

- 0b0000=미지원

- 0b0001=지원 (SCTLR_EL1.E0E 비트로 엔디안 설정)

- SNSMem

- 시큐어와 non-시큐어 메모리 분리 지원 여부

- 0b0000=미지원

- 0b0001=지원

- BigEnd

- Mixed 엔디안 지원

- 0b0000=미지원

- 0b0001=지원 (SCTLR_ELx.E0E 비트로 엔디안 설정)

- PARange

- 물리 주소 지원 범위

- 0b0000=32 bits, 4GB

- 0b0001=36 bits, 64GB

- 0b0010=40 bits, 1TB

- 0b0011=42 bits, 4TB

- 0b0100=44 bits, 16TB

- 0b0101=48 bits, 2n56TB

- 0b0110=52 bits, 4PB (ARMv8.2-LPA 필요)

- ASIDBits

- ASID 지원 비트 수

- 0b0000=8bits

- 0b0010=16bits

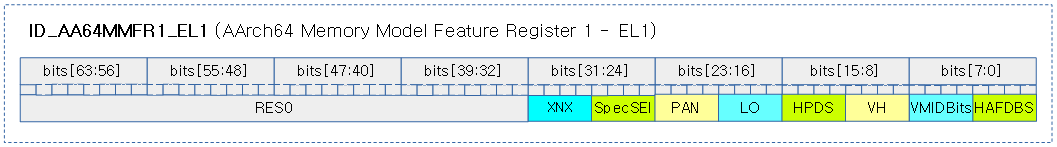

ID_AA64MMFR1_EL1 (Memory Model Feature Register 1 – EL1)

AArch64 상태에서 지원되는 메모리 모델을 알아오는 레지스터 1 이다.

- XNX

- ARMv8.2 Execute Never Control 지원 여부

- 0=not support

- 1=support

- SpecSEI

- ARMv8.2 RAS 사용시 Speculative 읽기시 SError 발생 지원 여부

- 0=not support, 1=support

- PAN

- ARMv8.1 PAN(Privileged Access Never) 지원 여부

- 0=not support

- 1=support (only for ARMv8.1)

- 2=support 및 AT S1E1RP 및 AT S1E1WP, AT S1E1 명령 지원 (only for ARMv8.2)

- LO

- LORegions 지원 여부

- 0=not support, 1=support

- HPDS

- ARMv8.1 변환 테이블에서 HPDS(Hierarchical Permission Disables Support) 기능 지원 여부

- 0=not support

- 1=support

- 2=support 및 마지막 단계 테이블의 bits[62:59]의 하드웨어 할당 가능

- VH

- ARM8.1 Virtualization Host Entension 기능 지원 여부

- 0=not support

- 1=support (only for ARMv8.1)

- VMIDBits

- ARMv8.1 VMID에 사용하는 비트 수

- 0=8 bits, 2=16 bits

- HAFDBS

- ARMv8.1 변환 테이블에서 HAFDBS(Hardware updates to Access Flag and Dirty Bit State) 기능 지원 여부

- 0=not support

- 1=access flag 지원

- 2=access flag 및 dirty state 지원

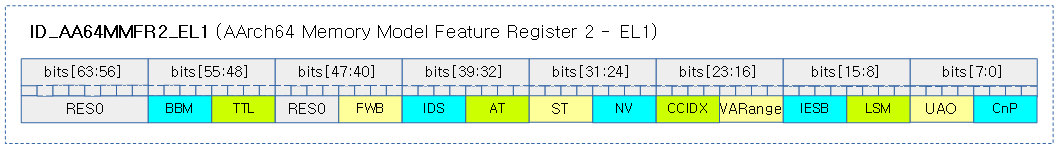

ID_AA64MMFR2_EL1 (Memory Model Feature Register 1 – EL1)

AArch64 상태에서 지원되는 메모리 모델을 알아오는 레지스터 2 이다.

- BBM

- ARMv8.4 변환을 위한 블럭 사이즈 변경 시 BBM(Break Before Make) 기능 지원 레벨

- 0=level 0 support

- 1=level 1 support

- 2=level 2 support

- TTL

- ARMv8.4 TTL 기능

- 0=bits[47:44]를 0으로 변환

- 1=bits[47:44] 변환 없이

- FWB

- ARMv8.4 HCR_EL2.FWB 기능 지원 여부

- 0=not support, 1=support

- IDS

- ARMv8.4 ID Space에 접근 시 아래 레지스터 값에 따른 exception 발생

- 0=ESR_ELx.EC==0

- 1=ESR_ELx.EC==0x18

- AT

- ARMv8.4 비정렬 single-copy atomic 기능 지원 여부

- 0=not support

- 1=support (16 byts)

- ST

- ARMv8.4 small 변환 테이블 지원

- 0=TCR_ELx.{T0SZ, T1SZ} 과 VTCR_EL2.T0SZ 필드의 최고 값은 39

- 1=TCR_ELx.{T0SZ, T1SZ} 과 VTCR_EL2.T0SZ 필드의 최고 값은 48 (단 64K granules시 47)

- NV

- ARMv8.4 NV(Nested Virtualization) 지원 여부

- 0=not support

- 1=HCR_EL2.{NV, NV1, AT} 지원 (for ARMv8.3)

- 2=HCR_EL2.{NV, NV1, NV2, AT} 및 VNCR_EL2 지원

- CCIDX

- ARMv8.3 CCSIDR_EL1 레지스터 포맷

- 0=32 비트, 1=64 비트

- VARange

- ARMv8.2 큰 가상 주소 지원 여부

- 0=48 비트, 1=64K granule 시 52 비트, 그 외 48 비트 (for ARMv8.2-LVA)

- IESB

- ARMv8.2 SCTLR_ELx.IESB 비트 지원 여부

- 0=not support, 1=support

- LSM

- ARMv8.2 SCTLR_EL{1, 2} 레지스터에서 LSMAOE 및 nTLSMD 필드 지원 여부

- 0=not support, 1=support

- UAO

- ARMv8.2 UAO(User Access Override) 기능 지원 여부

- 0=not support, 1=support

- CnP

- ARMv8.2 CnP(Common Not Private) 변환 기능 지원 여부

- 0=not support, 1=support

MMFR1_EL1 (Memory Model Feature Register 1 – EL1)

AArch32 상태에서 지원되는 메모리 모델을 알아오는 레지스터 1 이다.

- 참고: | ARM

- BPred

- 0=no branch predict

- 1=다음 상황에서 branch predict 플러시를 요청한다.

- 주소 변환 스테이지의 활성화/비활성화시

- 명령어 변경시

- 새로운 변환 테이블 매핑시

- TTBR0/1 및 TTBCR 레지스터 변경시

- ContextID 및 ASID 변경시

- 2=다음 상황에서 branch predict 플러시를 요청한다. (for ARMv8-A)

- 주소 변환 스테이지의 활성화/비활성화시

- 명령어 변경시

- 새로운 변환 테이블 매핑시

- 해당 ContextID 및 ASID 변경 없이 TTBR0/1 및 TTBCR 레지스터 변경시

- 3=명령어 변경시에만 branch predict 플러시를 요청한다. (for ARMv8-A)

- 4=어떠한 경우에도 branch predict 플러시를 요청하지 않는다. (for ARMv8-A)

- L1TstCin

- L1 데이터 캐시 테스트 & 클린

- 0=none support (only for ARMv8-A)

- 1=test & clean 지원

- 2=test & clean, test, clean, invalidate 지원

- L1Uni

- L1 통합 캐시 지원

- 0=none supported (only for ARMv8-A)

- 1=캐시의 invalidate 지원

- 2=캐시의 invalidate, clean 및 clean & invalidate 지원

- L1Hvd

- L1 하버드 캐시 지원

- 0=none support (only for ARMv8-A)

- 1=명령 캐시만 invalidate 지원

- 2=명령 및 데이터 캐시의 invalidate 지원

- 3=명령 및 데이터 캐시의 invalidate 및 clean & invalidate 지원

- L1UniSW

- L1 통합 캐시의 Set/Way 조작 지원

- 0=none supported (only for ARMv8-A)

- 1=clean 캐시 지원

- 2=clean 및 clean & invalidate 지원

- 3=clean, clean & invalidate 및 invalidate 지원

- L1HvdSW

- L1 하버드 캐시의 Set/Way 조작 지원

- 0=none supported (only for ARMv8-A)

- 1=clean 및 clean & invalidate 데이터 캐시 지원

- 2=clean, clean & invalidate 및 invalidate 데이터 캐시 지원

- 3=clean, clean & invalidate 및 invalidate 데이터 캐시 및 명령 캐시 invalidate 지원

- L1UniVA

- L1 통합 캐시의 가상 주소(VA)를 사용하여 조작 지원

- 0=none supported (only for ARMv8-A)

- 1=clean, invalidate 및 clean & invalidate 캐시 지원

- 2=clean, invalidate 및 clean & invalidate 캐시, 그리고 branch predictor invalidate 지원

- L1HvdVA

- L1 하버드 캐시의 가상 주소(VA)를 사용하여 조작 지원

- 0=none supported (only for ARMv8-A)

- 1=clean, invalidate 및 clean & invalidate 데이터 캐시, invalidate 명령 캐시 지원

- 2=clean, invalidate 및 clean & invalidate 데이터 캐시, invalidate 명령 캐시, 그리고 branch predictor invalidate 지원

시스템 제어

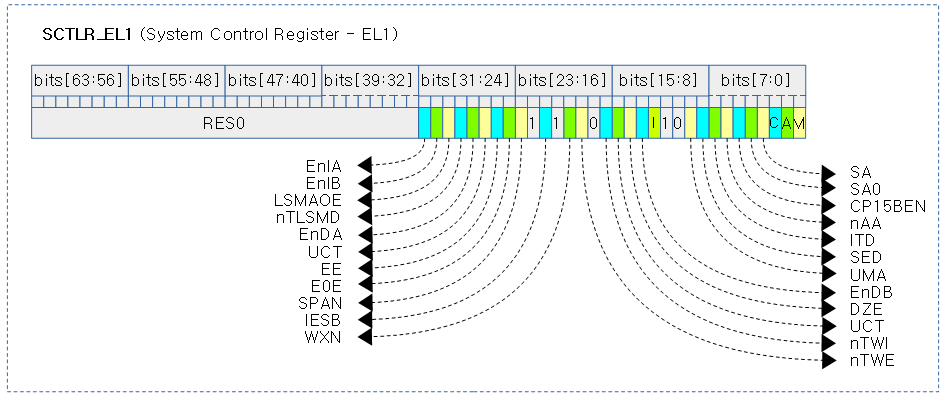

SCTLR_EL1 (System Control Register – EL1)

EL1 모드를 설정하기 위한 시스템 콘트롤 레지스터이다.

- 참고: SCTLR_EL1, System Control Register (EL1) | ARM

- EnIA

- ARMv8.3 APIAKey_EL1 Key 사용 PA(Pointer Authentification) 기능 활성화 여부

- 0=disable

- 1=enable

- EnIB

- ARMv8.3 APIBKey_EL1 Key 사용 PA(Pointer Authentification) 기능 활성화 여부

- 0=disable

- 1=enable

- LSMAOE

- ARMv8.2-LSMAOC(Load/Store Multiple Atomicity and Ordering Enable) 기능 활성화 여부

- 0=disable

- 1=enable

- nTLSMD

- ARMv8.2-LSMAOC 기능의 디바이스 메모리 No Trap 활성화 여부

- 0=disable, fault 발생

- 1=enable

- EnDA

- ARMv8.3 APDAKey_EL1 Key 사용 PA(Pointer Authentification) 기능 활성화 여부

- 0=disable

- 1=enable

- UCI

- EL0에서 EL1 캐시 조작 명령어 수행시 트랩 여부

- 0=trap

- 1=no trap

- EE

- EL1 엔디안 설정

- 0=리틀 엔디안

- 1=빅 엔디안

- E0E

- EL0 엔디안 설정

- 0=리틀 엔디안

- 1=빅 엔디안

- SPAN

- ARMv8.1 PAN(Privileged Access Never) 기능 동작시 PSTATE.PAN 동작 여부

- 0=익셉션 발생시 PSTATE.PAN=1 설정

- 1=익셉션 발생시 PSTATE.PAN 변경 없다.

- IESB

- ARMv8.2-IESB 기능의 Implicit Error Synchronization 이벤트 활성화 여부

- 0=disable

- 1=enable

- WXN

- 쓰기 권한이 XN(Excute Never) 권한을 내포하는지 여부

- 0=disable

- 1=enable

- SA

- SP 정렬 체크 활성화 여부

- 0=disable

- 1=enable (16바이트)

- nTWE

- EL0에서 WFE 명령 사용시 EL2로 No 트랩 여부

- 0=trap

- 1=no trap

- nTWI

- EL0에서 WFI 명령 사용시 EL2로 No 트랩 여부

- 0=trap

- 1=no trap

- UCT

- EL0에서 CTR_EL0 접근시 EL1으로 No 트랩 여부

- 0=trap

- 1=no trap

- DZE

- EL0에서 DC ZVA 명령 사용시 EL1으로 No 트랩 여부

- 0=trap

- 1=no trap

- EnDB

- ARMv8.3 APDBKey_EL1 Key 사용 PA(Pointer Authentification) 기능 활성화 여부

- 0=disable

- 1=enable

- I

- 명령 캐시 활성화 여부

- 0=disable

- 1=enable

- UMA

- EL0에서 MSR/MRS 명령으로 PSTATE.DAIF 접근시 EL1으로 No 트랩 여부

- 0=trap

- 1=no trap

- SED

- AArch32 EL0에서 SETEND 명령 disable 여부

- 0=enable

- 1=disable, undefined instruction으로 취급

- ITD

- AArch32 EL0에서 IT 명령 disable 여부

- 0=enable

- 1=disable, undefined instruction으로 취급

- nAA

- ARMv8.4-LSE 기능의 Non-Aligned Access 활성화 여부

- 0=disable, fault 발생

- 1=enable, fault 발생하지 않는다.

- CP15BEN

- EL0에서 CP15 메모리 베리어 활성화 여부

- 0=disable, undefined instruction으로 취급

- 1=enable

- SA0

- EL0에서 SP 정렬 체크 활성화 여부

- 0=disable

- 1=enable (16 바이트 미정렬시 exception 발생)

- SA

- EL1에서 SP 정렬 체크 활성화 여부

- 0=disable

- 1=enable (16 바이트 미정렬시 exception 발생)

- C

- 데이터 캐시 활성화 여부

- 0=disable

- 1=enable

- A

- 정렬 체크 활성화 여부

- 0=disable

- 1=enable, fault 발생

- M

- MMU 활성화 여부

- 0=disable

- 1=enable

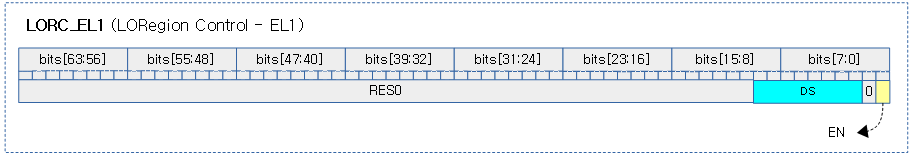

LORC_EL1, LORegion Register (EL1)

LORegion을 활성화하는 레지스터이다.

- 참고: LORC_EL1, LORegion Control (EL1) | ARM

- DS

- ARMv8.1 DS(Descriptor Select)

- 0~255

- EN

- LORegions 기능 활성화 여부

- 0=disable, 1=enable

GIC

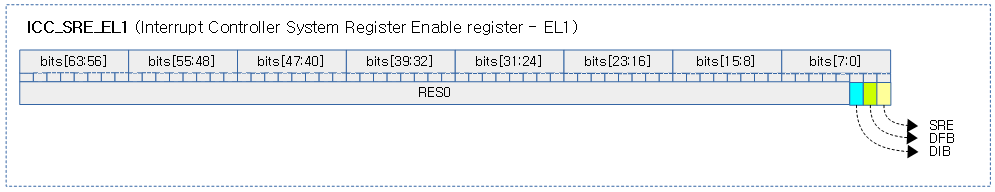

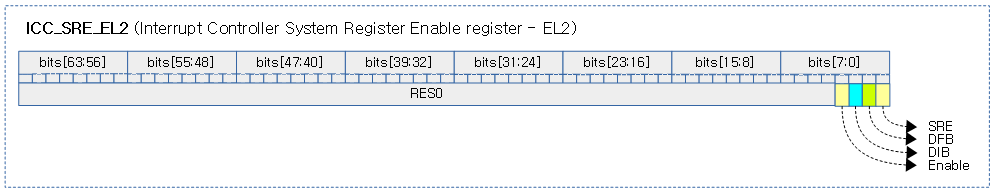

ICC_SRE_EL2 (Interrupt Controller System Register Enable Register – EL2)

인터럽트 컨트롤러 시스템 레지스터를 enable하는 레지스터이다.

- DIB

- Disable IRQ Bypass 기능 활성화 여부

- 0=enable, 1=disable

- DFB

- Disable FIQ Bypass 기능 활성화 여부

- 0=enable, 1=disable

- SRE

- GIC에 대한 시스템 레지스터(ICC_*) 활성화 여부

- 0=disable, 메모리 맵드 방식으로 사용해야 하고, ICC_로 시작하는 시스템 레지스터들의 접근시 el1에 트랩된다.

- 1=enable

하이퍼 바이저 관련 레지스터

시스템 설정

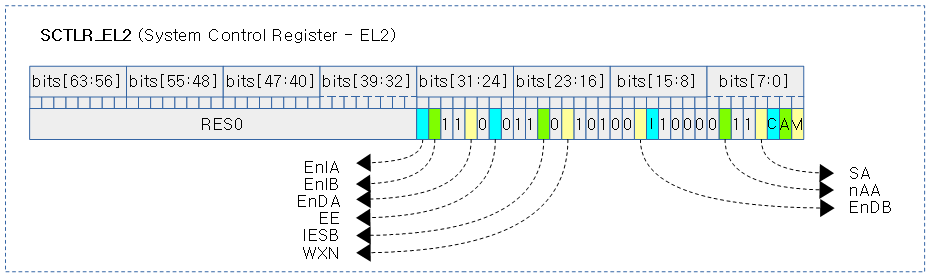

SCTLR_EL2 (System Control Register – EL2)

하이퍼 바이저 모드를 설정하기 위한 시스템 콘트롤 레지스터이다.

- 참고: SCTLR_EL2, System Control Register (EL2) | ARM

- EnIA

- ARMv8.3 APIAKey_EL1 Key 사용 PA(Pointer Authentification) 기능 활성화 여부

- 0=disable

- 1=enable

- EnIB

- ARMv8.3 APIBKey_EL1 Key 사용 PA(Pointer Authentification) 기능 활성화 여부

- 0=disable

- 1=enable

- EnDA

- ARMv8.3 APDAKey_EL1 Key 사용 PA(Pointer Authentification) 기능 활성화 여부

- 0=disable

- 1=enable

- EE

- 엔디안 설정

- 0=리틀 엔디안

- 1=빅 엔디안

- IESB

- ARMv8.2-IESB 기능의 Implicit Error Synchronization 이벤트 활성화 여부

- 0=disable

- 1=enable

- WXN

- 쓰기 권한이 XN(Excute Never) 권한을 내포하는지 여부

- 0=disable

- 1=enable

- EnDB

- ARMv8.3 APDBKey_EL1 Key 사용 PA(Pointer Authentification) 기능 활성화 여부

- 0=disable

- 1=enable

- I

- 명령 캐시 활성화 여부

- 0=disable

- 1=enable

- nAA

- ARMv8.4-LSE 기능의 Non-Aligned Access 활성화 여부

- 0=disable, fault 발생

- 1=enable, fault 발생하지 않는다.

- SA

- SP 정렬 체크 활성화 여부

- 0=disable

- 1=enable (16바이트)

- C

- 데이터 캐시 활성화 여부

- 0=disable

- 1=enable

- A

- 정렬 체크 활성화 여부

- 0=disable

- 1=enable, fault 발생

- M

- MMU 활성화 여부

- 0=disable

- 1=enable

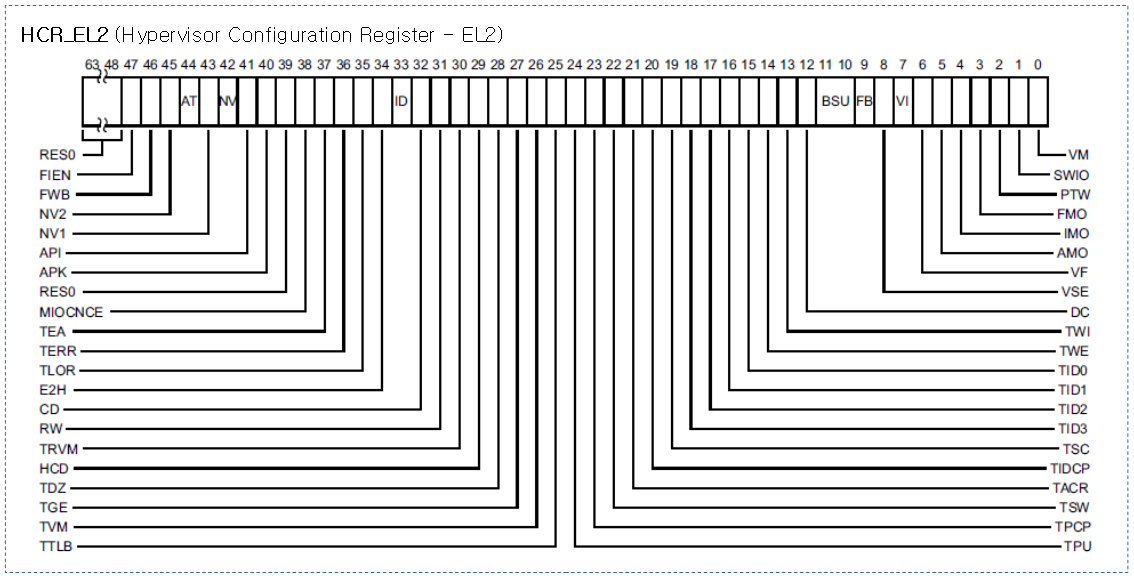

HCR_EL2 (System Control Register – EL2)

하이퍼 바이저를 설정하기 위한 시스템 콘트롤 레지스터이다.

- TEA

- 동기 외부 abort exceptin을 EL2로 라우트

- 0=disable, 1=enable (route to el2)

- E2H

- Host 운영체제가 EL2에서 동작하도록 설정

- 0=disable, 1=enable

- ID

- Stage 2에서의 명령 캐시 disable for el1&0

- 0=no effect

- 1=effect

- CD

- Stage 2에서의 데이터 캐시 disable for el1&0

- 0=no effect, 1=effect

- TGE

- el0 에서 el2로 TGE(Trap General Exception)

- 0=no effect, 1=effect

- AMO

- 물리 SError 라우팅

- IMO

- 물리 IRQ 라우팅

- FMO

- 물리 FIQ 라우팅

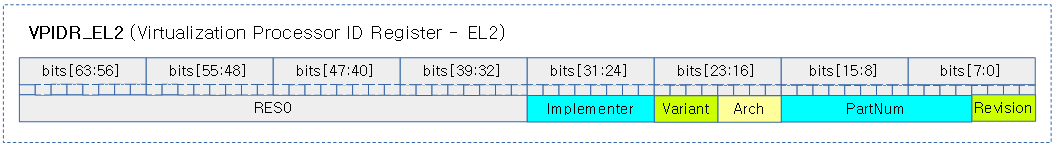

VPIDR_EL2 (Virtualization Processor ID Register – EL2)

Multiprocessor ID를 담은 레지스터이다.

- MIDR_EL1 참고

VMPIDR_EL2 (Virtualization Multiorocessor ID Register – EL2)

Virtualization Multiprocessor ID를 담은 레지스터이다.

- MPIDR_EL1 참고

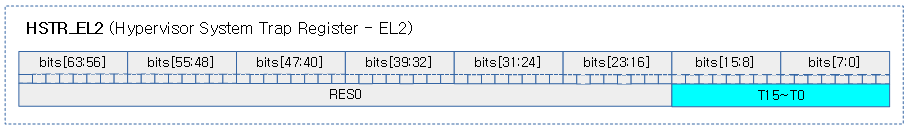

HSTR_EL2 (Hypervisor System Trap Register – EL2)

EL0&1에서 coprocess(MCR, MRC, MCRR, and MRRC) 접근 명령 사용시 발생되는 el2로의 트랩 제어 레지스터이다.

- T<n>

- CP15, C<n>에 접근하는 코프로세서 명령에 대해 el2로 트랩 발생

- 0=no trap, 1=trap

- T14와 T4는 RES0

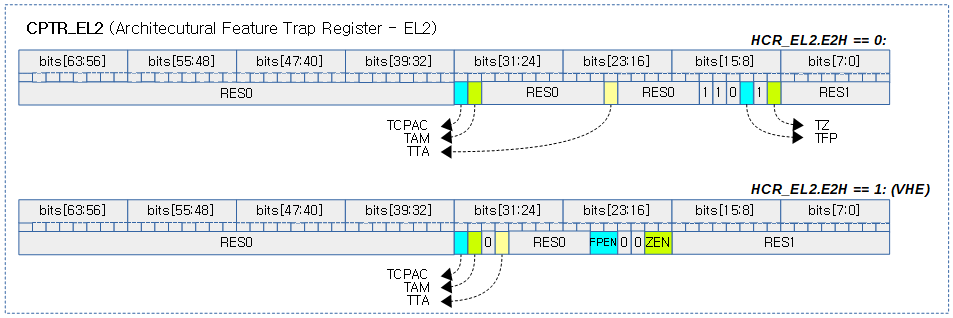

CPTR_EL2 (Architectural Feature Trap Register – EL2)

CPACR, CPACR_EL1, 트레이스 펑션, SVE, Advanced SIMD 및 실수 펑션 사용시 el2로 트랩을 제어하는 레지스터이다.

- TFP

- SVE, A-SIMD, 실수 펑션 사용시 el2로 트랩 발생

- 0=no trap, 1=trap

- TZ

- SVE 레지스터를 액세스할 때 el2로 트랩 발생

- 0=no trap, 1=trap

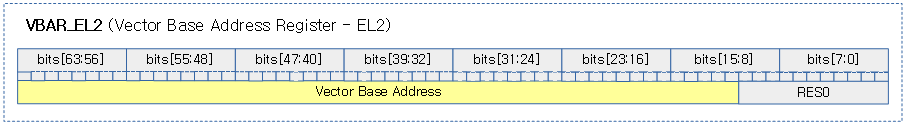

VBAR_EL2, Vector Base Address Register (EL2)

exception 벡터 베이스 주소를 지정하는 레지스터이다.

Stage 2 변환 테이블

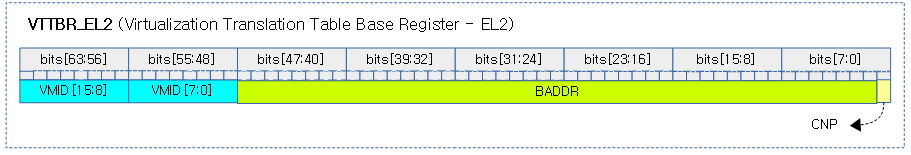

VTTBR_EL2 (Virtualization Translation Table Base Register – EL2)

stage 2의 페이지 테이블을 가리키는 레지스터이다.

- VMID[15:8]

- ARMv8.1-VMID16 지원시 상위 8비트를 기록하여 사용한다.

- VMID[15:8]

- 변환 테이블을 위한 VMID

- BADDR

- 변환 테이블 물리 주소

- CnP

- ARMv8.2-TTCNP 기능이 있는 경우 CnP(Common not Private) 기능 지원 여부

- 0=변환 테이블의 엔트리는 현재 PE에만 적용한다.

- 1=변환 테이블의 엔트리는 Inner Share의 다른 PE와 공유한다.

하이퍼 바이저 카운터

아키텍처 타이머 및 카운터 레지스터의 사용법은 간단하나 종류가 여러 가지 있다.

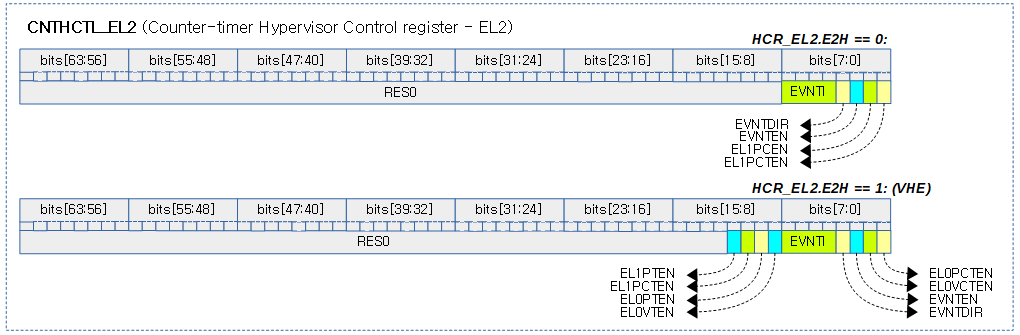

CNTHCTL_EL2 (Counter-timer Hypervisor Control Register – EL2)

EL0&1 physical 카운터와 타이머에 접근하기 위한 콘트롤 레지스터이다.

- EL1PTEN

- HCR_EL2.TGE==0인 경우, EL0&1에서 EL1 물리 타이머 액세스시 EL2로 트랩 발생

- 0=enable, 1=disable

- EL1PCTEN

- HCR_EL2.TGE==0인 경우, EL0&1에서 EL1 물리 카운터 액세스시 EL2로 트랩발생

- 0=enable, 1=disable

- EL0PTEN

- HCR_EL2.TGE==1인 경우, EL0에서 EL0 물리 타이머 액세스시 EL2로 트랩 발생

- 0=enable, 1=disable

- EL0VTEN

- HCR_EL2.TGE==1인 경우, EL0에서 EL0 가상 타이머 액세스시 EL2로 트랩발생

- 0=enable, 1=disable

- EVNTI

- CNTPCT_EL0 카운터의 어떠한 비트(0~15)에서 이벤트가 발생될지 선택한다.

- ENNTDIR

- CNTPCT_EL0 카운터의 해당(EVNTI) 비트의 트리거 방향을 제어한다.

- 0=high edge시 트리거

- 1=low edge시 트리거

- EVNTEN

- CNTPCT_EL0 카운터로부터 이벤트 스트림 발생 여부 제어

- 0=disable, 1=enable

- EL0VCTEN

- HCR_EL2.TGE==1인 경우, EL0에서 EL0 가상 카운터 액세스시 EL2로 트랩발생

- 0=enable, 1=disable

- EL0PCTEN

- HCR_EL2.TGE==1인 경우, EL0에서 EL0 물리 카운터 액세스시 EL2로 트랩 발생

- 0=enable, 1=disable

CNTVOFF_EL2 (Counter-timer Hypervisor Control Register – EL2)

물리 카운터(CNTPCT_EL0)에 대한 Virtual Offset을 담고 있는 콘트롤 레지스터이다.

하이퍼 바이저 GIC

ICC_SRE_EL2 (Interrupt Controller System Register Enable Register – EL2)

인터럽트 컨트롤러 시스템 레지스터를 enable하는 레지스터이다.

- Enable

- 더 낮은 EL에서 ICC_SRE_EL1 접근을 가능하게 할지 여부

- 0=disable, non-secure EL1에서 ICC_SRE_EL1 접근시 EL2로 트랩 발생

- DIB

- Disable IRQ Bypass 기능 활성화 여부

- 0=enable, 1=disable

- DFB

- Disable FIQ Bypass 기능 활성화 여부

- 0=enable, 1=disable

- SRE

- GIC에 대한 시스템 레지스터(ICC_*) 활성화 여부

- 0=disable, 메모리 맵드 방식으로 사용해야 하고, ICC_ 및 ICH_로 시작하는 시스템 레지스터들의 접근시 el2에 트랩된다.

- 1=enable

문영일 선배님, 안녕하세요.

훌륭한 블로그 자료를 감사히 잘 읽고 있습니다. 블로그의 글을 읽다가 오타로 보이는 내용이 있는 것 같아 제보드립니다.

1. CTR_EL0 레지스터의 IminLine 필드는 인스트럭션 캐시를 설정하는 내용으로 보입니다.

‘데이터 캐시 -> 명령 캐시’ 인 것 같아 보입니다.

2. CTytpe7이 오타로 보입니다.

‘CType1 ~ CTytpe7’ -> ‘CType1 ~ CType7’

한번 참고 부탁드립니다.

Austin Kim님, 안녕하세요?

종종 Arm Linux Kernel Hacks에 방문해서 유익한 글을 잘 보고 있습니다.

그리고 오타 찾아주셔서 감사합니다. ^^