최근 PC 및 Embedded 시스템에서 가장 많이 사용하는 고속 Bus인 PCI Express를 위주로 설명한다. 먼저 PCI Bus에 대해 간략히 알아보고 PCI Express를 더 자세히 비교하여 설명하기로 한다.

PCI

PCI(Peripheral Component Interconnect) 아키텍처는 주변 장치 연결을 위해 ISA(Industry Standard Architecture bus), EISA, MCA, VESA 등의 버스 표준을 대체하기 위해 설계되었다. 오늘날 PC에서 가장 널리 사용되는 버스 규격이다.

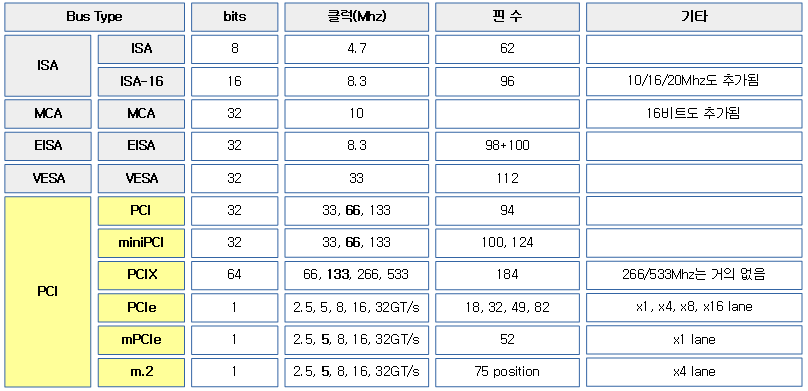

다음 그림은 버스 타입별로 비트 수, 클럭 및 핀 수를 비교하였다.

PCI는 다음과 같은 주요 목표로 설계되었다.

- 더 빠른 전송 속도의 달성

- 33Mhz 클럭부터 시작하여 66Mhz까지가 가장 많이 사용된다. (25Mhz 시스템도 있다.)

- PCI/X에서는 66Mhz, 133Mhz, 266Mhz 등으로 발전되었다. (533Mhz 도 시도되었다.)

- 플랫폼 독립성

- 일부 플랫폼에 종속되지 않고 대부분의 플랫폼에서 사용된다.

- 예) x86, IA-32, IA-64, Alpha, MIPS, PowerPC, ARM, …

- 디바이스 추가/제거의 편이성

- 버스에 장치가 쉽게 연결되고 해제될 수 있는 구조를 채택하였다.

PCI와 ISA(EISA)와의 연동 관계

32비트 PC가 처음 출현했을 때 사용하던 방식으로 ISA 호환을 위해 PCI 버스 하단에서 ISA 버스를 지원함을 알 수 있다.

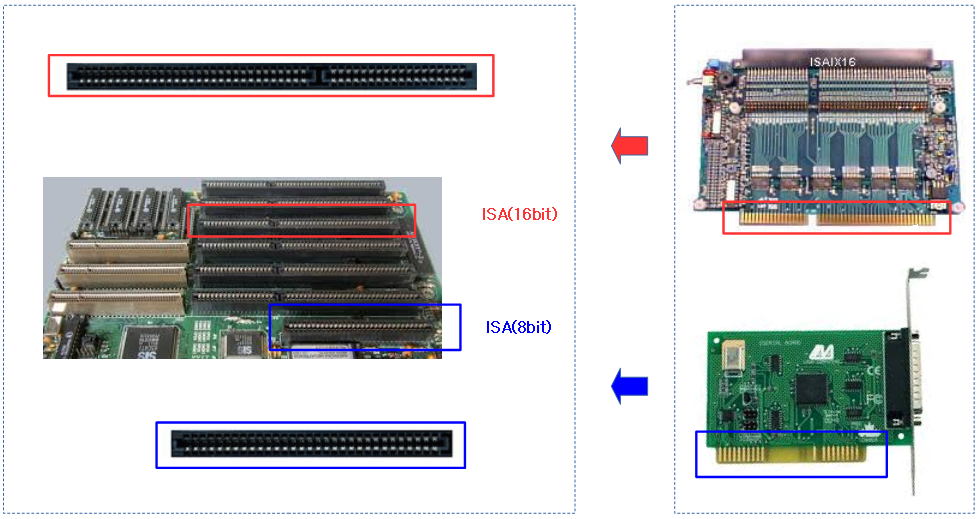

ISA 슬롯

8비트 및 16비트 ISA 버스가 채택된 ISA 슬롯 모습을 알아본다.

- 16비트 ISA 슬롯은 16비트 ISA 카드 및 8비트 ISA 카드 둘 다 지원한다.

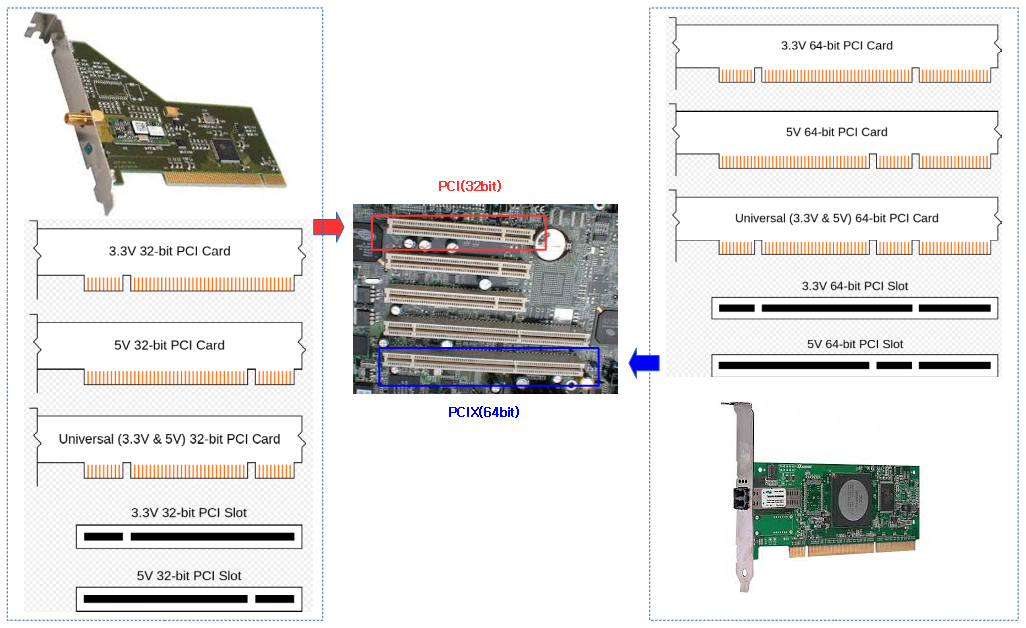

PCI & PCI/X 슬롯

32비트 PCI 및 64비트 PCI 버스가 채택된 PCI 및 PCI/X 슬롯 모습을 알아본다.

- 64비트 PCI/X 슬롯은 64비트 PCI/X 카드 및 32비트 PCI 카드 둘 다 지원한다.

- PCI 및 PCI/X 슬롯이 지원하는 전압(Volatage)을 구분할 수 있도록 슬롯에 홀(Hole)의 위치를 바꿔 종류가 다른 카드가 꽂히지 않게 하였다.

- 아래 예)

- 5V PCI 슬롯 3개

- 3.3V PCI/X 슬롯 2개

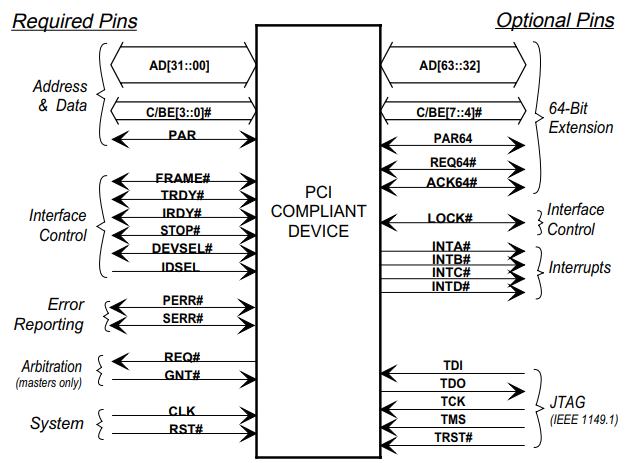

PCI 핀

1 ~ 수 개의 pci 슬롯을 통해 pci 버스를 공유한다.

- PCI 버스는 4개의 legacy 인터럽트 라인을 지원한다. (INTA#, INTB#, INTC#, INTD#)

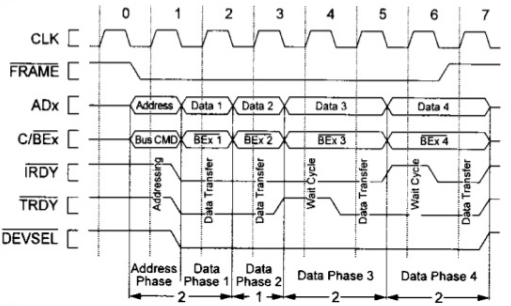

PCI 전송

다음은 버스 컨트롤러가 발생시키는 시그널 라인들에 대한 설명이다. (# 기호는 low active로 동작함을 의미한다.)

- CLK

- 33/66Mhz 기반 클럭(CLK) 시그널

- 고정 주기로 클럭이 발생되며 rising edge 신호에 동기하도록 한다.

- RST#

- Reset

- 1ms 이상의 low active 시그널을 사용하여 pci 버스에 연결된 컨트롤러와 모든 pci 디바이스를 HW 리셋시킨다.

- 리셋이 해제된 후 5 사이클 이내에 각 디바이스들은 전송을 요청하면 안된다.

- IDSEL

- Initialization Device Select

- 타겟 디바이스가 이 시그널을 읽어 configuration 레지스터 중 하나를 읽을 때 사용된다.

버스 마스터가 발생시키는 시그널 라인들에 대한 설명이다.

- FRAME#

- 현재 initiator(버스 마스터)로부터 버스 엑세스가 시작되고 계속됨을 알리기 위해 low active 시그널을 발생한다.

- ADx

- Address / Data

- initiator가 시 분할 방법을 사용하여 32비트 주소 또는 데이터 비트 둘 중 하나를 출력한다.

- C/BEx#

- 명령 또는 바이트 enable

- Command

- initiator가 트랜잭션 타입을 정의하며 4 비트 조합을 사용한다. (C/BE0 ~ C/BE3)

- BE0# ~ BE3#

- 한 번에 보낼 수 있는 바이트를 지정한다. (low active)

- 예) BE3#=1, BE2#=1, BE1#=0, BE0#=0

- 하위 2 바이트만 전송한다.

- 예) BE3#=1, BE2#=1, BE1#=0, BE0#=0

- 한 번에 보낼 수 있는 바이트를 지정한다. (low active)

- Command

- 명령 또는 바이트 enable

- IRDY#

- Initiator Ready for data

- 현재 initiator(버스 마스터)가 AD# 및 C/BEx를 준비한 후 Ready되었음을 알리기 위해 low active 시그널을 발생한다.

- high일 때에는 idle 상태이다.

- 전송은 반드시 8 사이클 이내에 이루어져야 한다.

- LOCK#

- Initiator가 atomic 트랜잭션을 처리하기 위해 현재 타겟 디바이스를 고정(lock)하도록 low active 시그널을 발생한다.

다음 파란색 시그널은 타겟 디바이스가 발생시키는 시그널 라인들에 대한 설명이다. (# 기호는 low active로 동작함을 의미한다.)

- STOP#

- 데이터 전송 중 타겟 디바이스가 전송을 중단해달라고 요청할 때 low active 시그널을 발생한다.

- TRDY#

- Target Ready

- 타겟 디바이스가 응답하며, 준비되어 전송 가능한 상태에서 low active 신호를 시그널을 발생한다.

- DEVSEL#

- Device Select

- 타겟 디바이스가 자신이 선택되었음을 initiator에게 알리기 위해 low active 시그널을 발생한다.

- initiator가 6 사이클 이내에 이 시그널을 받지 못하면 취소된다.

- INTA# ~ INTD#

- 4개의 인터럽트 라인을 가지며 PCI 디바이스는 이 라인을 share하여 사용하며 인터럽트를 발생시킬 때 low active 시그널을 발생한다.

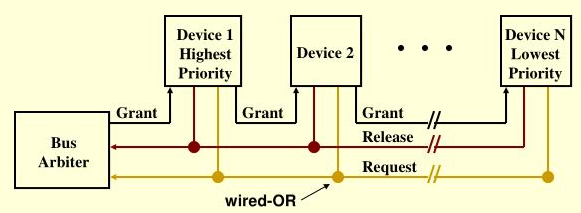

PCI Bus Arbiter

PCI Bus Arbiter의 구성은 다음과 같이 Centralized 또는 Daisy Chain 방식을 사용한다.

- Centralized Arbiter

- 별도의 회로이지만 보통 PCI host 또는 PCI 브리지에 통합되어있다.

- 여러가지 선택 알고리즘

- Fairness (default)

- 가장 중요한 디바이스를 우선 선택한다.

- 디바이스별 우선 순위에 의해 최대 Latency 레지스터를 설정한다. 그런 후 이 latency를 만족하도록 디바이스를 선택한다.

- FIFO

- 가장 먼저 요청한 디바이스 우선 선택

- RR

- 라운드 로빈 방식에 의한 선택

- Fairness (default)

- Daisy Chain Arbiter

- Arbiter에 가까운 슬롯에 위치한 디바이스가 먼저 선택된다.

다음 시그널은 PCI 버스 arbiter 회로가 수신또는 발생시키는 시그널 라인들에 대한 설명이다.

- REQ#

- 버스 사용 요청을 의미한다.

- 버스를 사용하고자 하는 버스 마스터 디바이스가 PCI bus Arbiter에 요청하며 여러 버스 마스터 디바이스가 동시 요청한 경우 GNT#를 통해 하나의 디바이스를 선택한다.

- 참고로 대부분의 PCI 디바이스들은 bus-master 기능을 갖는다. 이 들은 peer-to-peer 전송 및 DMA 전송을 위해 버스 요청을 할 때 다른 PCI 디바이스들과 버스를 차지하기 위해 경합(arbitration) 한다.

- GNT#

- PCI 버스 arbiter가 발생시키는 신호로 arbitration 상태에서 승리한 경우를 의미한다. 그런 경우 다음 시작 시 처리하게됨을 의미한다. (first request ownership)

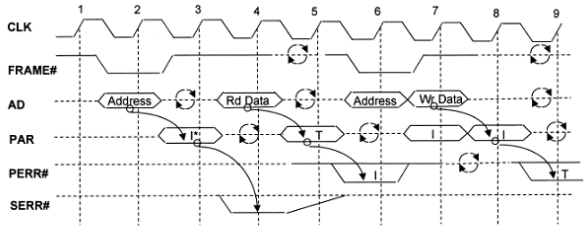

PCI 전송 에러 체크

PCI 전송 에러를 감지하는 회로이다. 오래된 pc에서는 단순하게 처리하기 위해 전송 에러를 감지하면 NMI를 발생시킨 후 시스템을 정지시키기도 했다.

- PAR

- Initiator가 Parity 부호로 마스터 버스가 짝수 사이클의 주소 및 데이터에 대해 parity 부호를 전송한다.

- PERR#

- Parity Error

- 타겟 디바이스가 짝수 사이클에 수신한 데이터와 그 다음 사이클에 받은 Parity 부호를 비교하여 문제가 발생하였을 때 PERR#에 low active 시그널을 발생시킨다.

- SERR#

- System Error

- 위와 동일하지만 타겟 디바이스가 데이터가 아닌 타겟 주소에 대한 전송에 문제가 발생했을 때 SERR#에 low active 시그널을 발생시킨다.

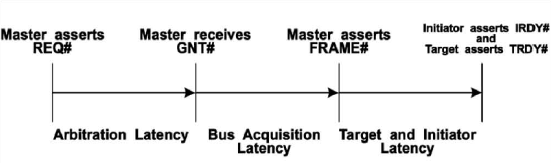

버스 접근 Latency

Bus Access Latency는 다음 3가지를 포함한다. 참고로 MLT(Master Latency Timer)는 configuration 레지스터 중 offset=14 바이트 위치에 있다.

- Arbitration Latency

- Bus Acquisition Latency

- 최대 16 클럭 이내

- Initiator and Target Latency

- 마스터의 경우 최대 8클럭 이내

- 타겟의 경우 최대 16클럭 이내

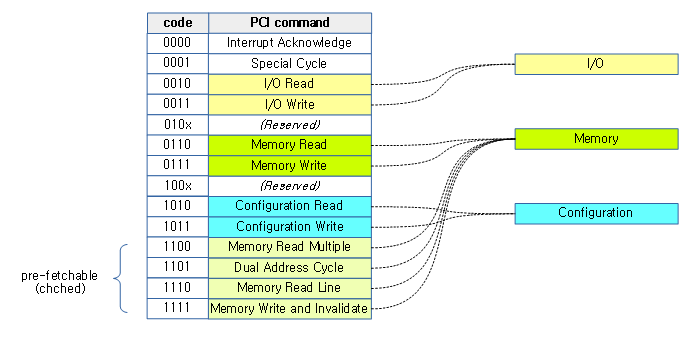

PCI Command – C/BE[3:0]#

4비트를 사용하여 명령 타입을 구분한다.

- Special Cycle

- AD[15:0]를 사용하여 메시지 전달

- 0000h

- Shutdown

- 0001h

- Halt

- 0000h

- AD[15:0]를 사용하여 메시지 전달

- Memory 영역에 대해서만 버스트 전송을 지원한다. (1100)

- Memory 영역에 대해서만 캐시 명령을 지원한다. (1110, 1111)

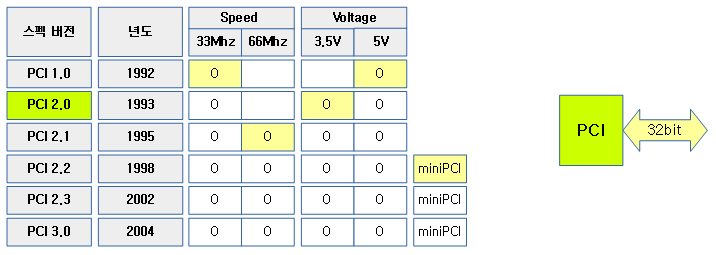

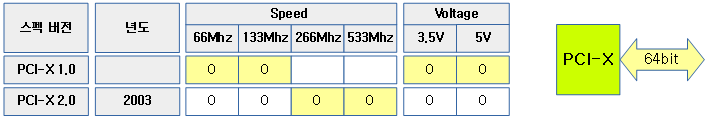

PCI History

PCI H/W는 다음과 같이 3가지 종류의 버스를 사용한다.

- PCI

- 병렬 32bit 버스

- PCI/X

- 병렬 64bit 버스

- PCIe

- 직렬 버스

PCI

- PCI 2.2 규격부터슬롯 크기를 줄인 miniPCI 규격이 추가로 발표되었다.

- PCI 버스 당 공유하여 사용할 수 있는 최대 슬롯 수

- 33Mhz: 4~5 슬롯

- 66Mhz : 1~2 슬롯

PCI/X

- PCIe로 대체되어 오늘날 거의 사용되지 않는다.

- PCI 버스 당 공유하여 사용할 수 있는 최대 슬롯 수

- 66Mhz: 4 슬롯

- 133Mhz: 1~2 슬롯

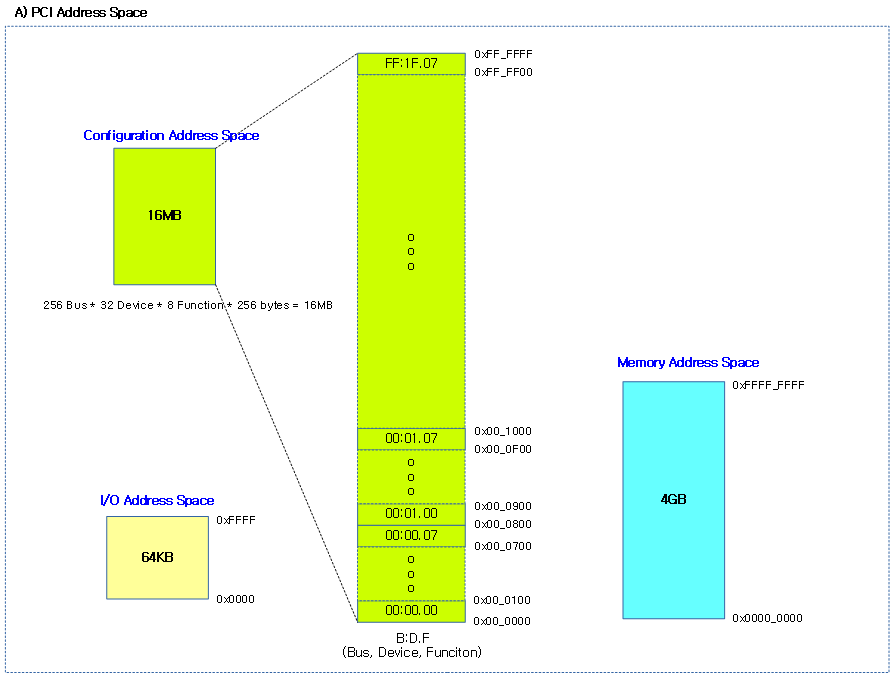

PCI Address Space Map

PCI는 다음과 같이 3가지 주소 영역을 지원한다. (주의: PCI 고유의 주소 공간이며 CPU가 access할 수 있는 물리 주소 영역이 아니다)

- PCI Configuration Address Space

- 16MB 영역의 PCI configuration 영역을 지원한다.

- 하나의 펑션 당 256 바이트를 지원한다.

- 버스(256) * 디바이스(32) * 펑션(8)

- 이 영역은 다음과 같은 API를 사용하여 접근할 수 있다.

- pci_read_config_byte() & pci_write_config_byte()

- pci_read_config_word() & pci_write_config_word()

- pci_read_config_dword() & pci_write_config_dword()

- PCI I/O Address Space

- 64K 영역의 I/O 메모리 주소 영역을 지원한다.

- x86등 특정 아키텍처에서 사용하는 IO 포트 주소에 매핑하여 접근할 수 있다.

- arm, arm64등 아키텍처가 IO 포트를 지원하지 않는 경우 PCI Memory와 동일하게 CPU의 물리 주소 공간에 노출시켜 사용할 수 있다.

- 리눅스 커널에서 물리 주소 공간에 노출된 이 영역을 사용할 때에는 가상 주소 공간에 매핑시켜 접근한다.

- PCI Memory Address Space

- 4G 영역의 메모리 주소 영역을 지원한다.

- CPU의 비어 있는 물리 주소 공간에 노출시켜 사용할 수 있다.

- 리눅스 커널에서 물리 주소 공간에 노출된 이 영역을 사용할 때에는 가상 주소 공간에 매핑시켜 접근한다.

Single Function & Multi Function Device

Single Function Device

- 하나의 물리 디바이스내에 하나의 기능을 가진 pci 디바이스

Multi Function Device

- 하나의 물리 디바이스내에 여러개의 function을 가진 pci 디바이스이다.

- 물리적으로 하나의 패키지로 묶여 있지만 각각의 function들은 별도의 pci 디바이스이다.

Legacy Interrupts

INTA ~ INTD 인터럽트 라인

- 싱글 펑션 디바이스의 경우 레거시 인터럽트를 사용하려면 INTA 라인만을 지정하여 사용할 수 있다.

- 멀티 펑션 디바이스의 경우 각각의 펑션은 레거시 인터럽트로 INTA ~ INTD 까지 4개의 인터럽트 라인 중 하나를 지정할 수 있다.

- 여러 개의 펑션이 하나의 인터럽트 라인을 공유하여 지정할 수도 있다.

- 예) 최대 8개의 펑션을 가진 pci 디바이스가 7개의 펑션이 INTA를 지정하고, 마지막 1개의 펑션만 INTB를 지정한다.

Legacy Interrupt 라우팅

시스템에 여러 개의 PCI 슬롯을 지원하는 경우 각 슬롯의 INTA ~ INTD 라인들의 라우팅은 시스템 설계에 따라 다르다.

- 독립된 인터럽트 라인

- 각각의 PCI 슬롯에 사용된 INTA ~ INTD 까지의 인터럽트를 인터럽트 컨트롤러의 인터럽트 라인에 중복되지 않도록 독립적으로 연결한다.

- 슬롯 1번 INTA, INTB, INTC, INTD -> 56, 57, 58, 59

- 슬롯 2번 INTA, INTB, INTC, INTD -> 60, 61, 62, 63

- 각각의 PCI 슬롯에 사용된 INTA ~ INTD 까지의 인터럽트를 인터럽트 컨트롤러의 인터럽트 라인에 중복되지 않도록 독립적으로 연결한다.

- 공유 인터럽트 라인

- 모든 슬롯의 INTA를 하나로 묶어 인터럽트 컨트롤러의 인터럽트 라인에 연결한다. 나머지 INTB ~ INTD도 같은 방식으로 연결하는 방법으로 4개의 인터럽트 라인만을 공유하여 사용한다.

- 슬롯 1번 INTA, INTB, INTC, INTD -> 56, 57, 58, 59

- 슬롯 2번 INTA, INTB, INTC, INTD -> 56, 57, 58, 59

- 모든 슬롯의 INTA를 하나로 묶어 인터럽트 컨트롤러의 인터럽트 라인에 연결한다. 나머지 INTB ~ INTD도 같은 방식으로 연결하는 방법으로 4개의 인터럽트 라인만을 공유하여 사용한다.

- Mixed 인터럽트 라인

- 위의 2 가지 방법을 섞어 구성한다.

MSI(Message Signaled Interrupt)

PCI 디바이스가 레거시 인터럽트 대신 MSI를 사용하면 다음과 같은 장점들이 있다.

- 인터럽트 라인의 트레이스(라우팅)가 필요 없다.

- 멀티 펑션 디바이스들이 같은 번호의 인터럽트 라인을 공유하여 사용할 필요없다.

- 디바이스 드라이버들 간의 인터럽트 chain이 필요없어진다.

PCI Express

PCI Express 버스는 여러 개의 슬롯을 공유하지 않고, 1 vs 1로 연결하여 사용한다. 이러한 특성으로 인해 여러 개의 슬롯이 필요한 경우 PCI express 스위치를 사용하여 확장한다.

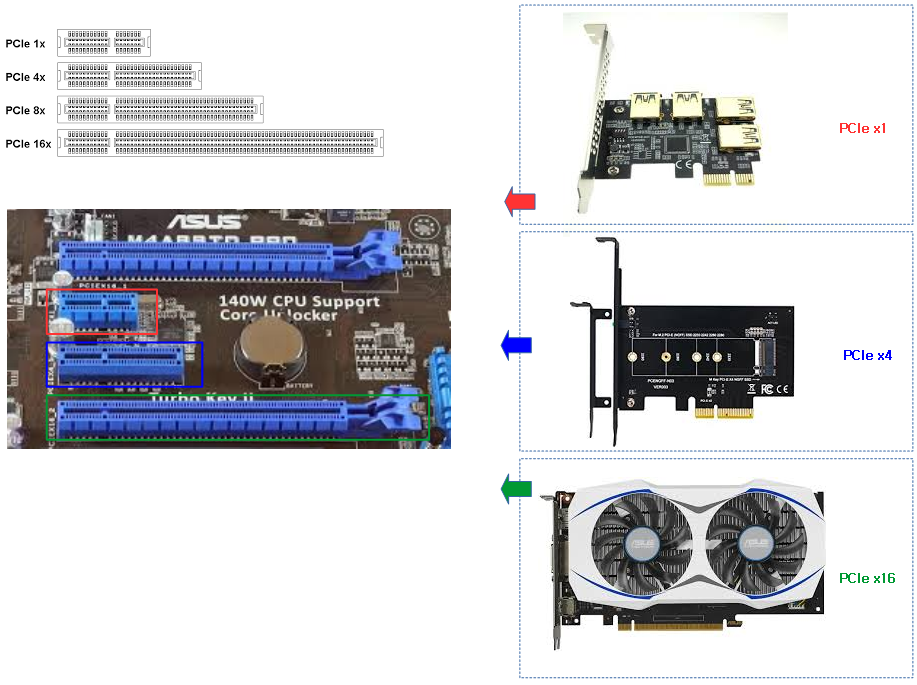

PCI Express 슬롯 (PCIe)

각각의 lane 수를 가지는 PCIe 슬롯 및 PCIe 카드를 알아본다.

- PCI Express 버스는 x1, x2, x4, x8, x12, x16, x32 레인을 지원한다.

- 표준 PCI Express 슬롯 형태로는 아래 그림과 같이 x1, x4, x8, x16 레인을 지원한다.

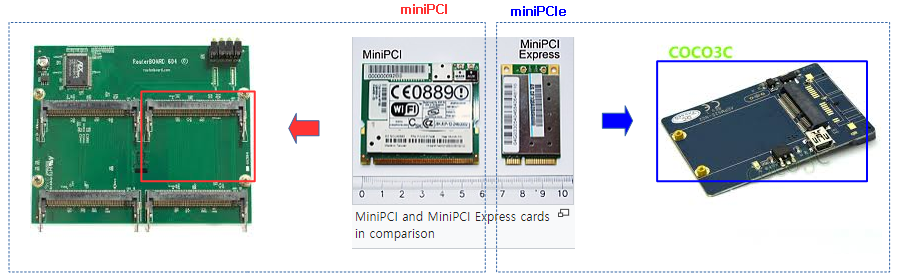

miniPCI 및 miniPCIe 슬롯

PCI 및 PCIe의 미니 사이즈로도 사용되고 있다. 이 폼팩터들은 점점 사용되지 않고 있으며 이들은 m.2 폼팩터로 사용 추세가 이동하고 있다.

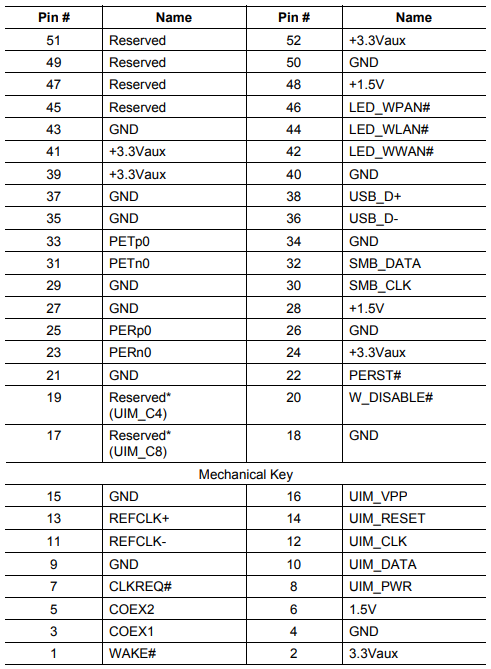

miniPCIe 핀

M.2

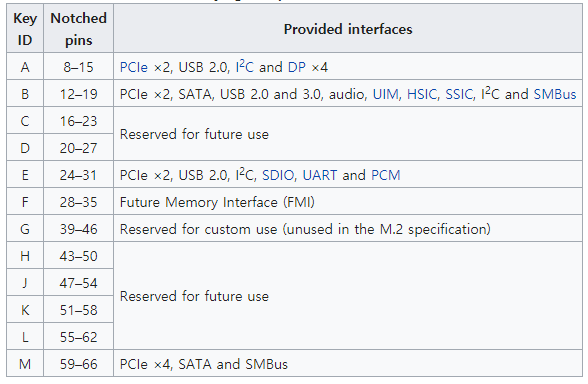

- m.2는 NGFF(Next Gen Form Factor)로 알려져 있으며 여러가지 버스들을 조합하여 제공한다.

- PCIe 3.0

- 기존 mPCIe 슬롯이 1개의 레인만을 지원한 것에 비해 최대 x4 레인을 지원한다.

- x2 레인을 지원하는 슬롯은 m.2 B key (양방향 4GB)

- x4 레인을 지원하는 슬롯은 m.2 M key (양방향 8GB)

- 기존 mPCIe 슬롯이 1개의 레인만을 지원한 것에 비해 최대 x4 레인을 지원한다.

- SATA 3.0

- 최대 6Gbps 속도

- USB 3.0

- 최대 5Gbps 속도

- 그 외

- USB 2.0, I2C, SMBus, DP x4, audio, UIM, SSIC, SDIO, UART, PCM, FMI

- PCIe 3.0

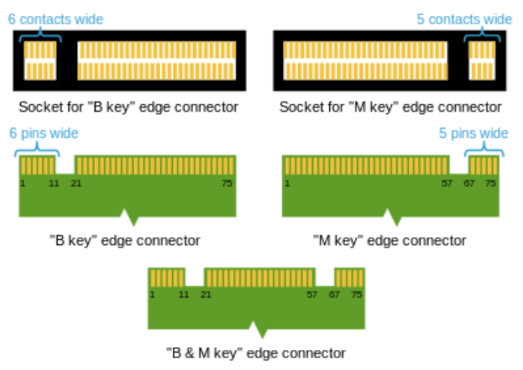

- keying

-

- 75개의 핀 포지션 중 key A ~ M 까지의 자리를 막아 구분한다.

-

- 표준 사이즈

- 폭(mm)

- 12, 16, 22, 30

- 길이(mm)

- 16, 26, 30, 38, 42, 60, 80, 110

- 두께(mm)

- 상면을 사용한 싱글 사이드 또는 상/하면을 사용한 더블 사이드

- 상면

- 1.20, 1.35, 1.50

- 하면

- 0.7, 1.35, 1.50

- 상면

- 상면을 사용한 싱글 사이드 또는 상/하면을 사용한 더블 사이드

- 예) WWLL-HH-K-[K]

- 2280 -> 폭은 22mm, 길이는 80mm

- D1 -> Double (상면은 1.20mm, 하면은 1.35mm)

- BM -> b key, m key

- 폭(mm)

M.2 Keying

M.2 소켓(슬롯)을 통해 여러 가지 버스를 제공하는데 이의 제공 여부 구분을 정의한다.

- M.2 소켓에서 Key ID에 맞는 핀들을 막았으므로 이 M.2 소켓에 연결할 수 있는 M.2 카드도 동일한 key ID를 보유해야 한다.

- M.2 슬롯은 1개의 key ID를 가진다.

- M.2 카드는 1~2 개의 key ID를 가지고 있다.

- 가장 많이 사용하는 M.2 소켓의 key ID는 다음과 같다.

- Key B

- M.2 소켓에서 B 포지션에 해당하는 12~19번 핀 자리에 핀들이 연결되지 못하게 연결 구멍을 막는다.

- B 포지션만 막는 제품은 많지 않고, 대부분 B+M을 사용한다. 이 경우 key M을 사용하는 카드도 허용되지만 x4 레인을 사용하지 못한다.

- M.2 소켓에서 B 포지션에 해당하는 12~19번 핀 자리에 핀들이 연결되지 못하게 연결 구멍을 막는다.

- Key M

- M.2 소켓에서 B 포지션에 해당하는 59~66번 핀 자리에 핀들이 연결되지 못하게 연결 구멍을 막는다.

- Key B

M.2 카드에서 가장 많이 사용하는 key ID는 다음과 같다.

- Key B+M

- M.2 카드에서 B 포지션 및 M 포지션에 해당하는 핀 자리를 hole 상태로 비워둔다.

- Key B 및 Key M을 사용하는 M.2 소켓에 연결할 수 있다.

- M.2 카드에서 B 포지션 및 M 포지션에 해당하는 핀 자리를 hole 상태로 비워둔다.

- Key M

- M.2 카드에서 M 포지션에 해당하는 핀 자리를 hole 상태로 비워둔다.

아래 그림을 보고 key B+M과 key M 타입을 구분하는 방법을 알아두자.

- 아래 카드 그림은 top면에서 볼때의 기준이다.

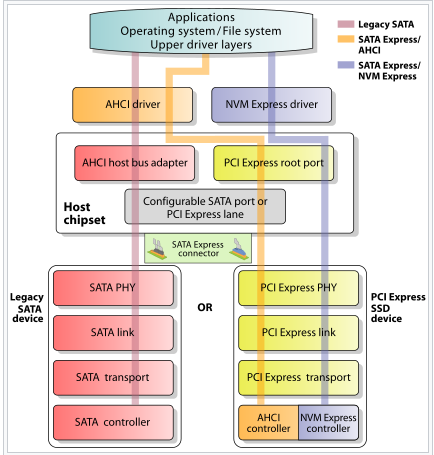

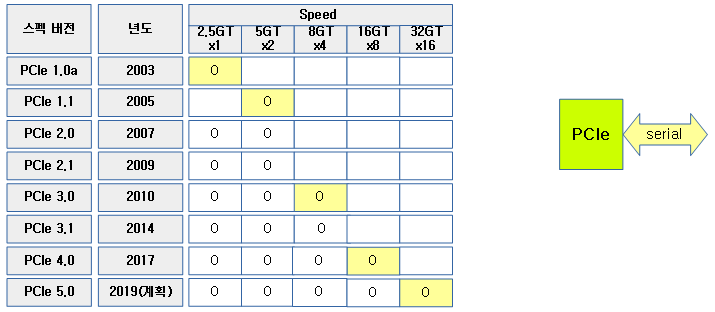

다음은 여러 가지 SSD 타입에 대해 설명하였다.

- SATA 커넥터

- AHCI 프로토콜을 채용한 드라이버를 사용하여 SATA 커넥터에 연결된 SSD를 사용한다.

- 예) 삼성 2.5인치 850 SATA SSD

- mSATA 커넥터

- AHCI 프로토콜을 채용한 드라이버를 사용하여 mSATAQ 커넥터에 연결된 SSD를 사용한다.

- 예) 삼성 850 EVO mSATA SSD

- M.2 커넥터 – M.2 SATA

- AHCI 프로토콜을 채용한 드라이버를 사용하여 M.2 커넥터의 SATA3 버스에 연결된 SSD를 사용한다.

- 예) 삼성 850 EVO M.2 2282 SSD

- 참고로 USB 3.0/3.1 등의 외장형 SSD 케이스에 포함되는 경우 대역폭이 모자라므로 M.2 SATA 타입의 SSD를 사용한다.

- M.2 커넥터 – M.2 PCIe AHCI

- AHCI 프로토콜을 채용한 드라이버를 사용하여 M.2 커넥터의 PCIe 버스에 연결된 SSD를 사용한다.

- 현재는 이 방식을 거의 사용하지 않는다.

- M.2 커넥터 – M.2 PCIe NVMe – 가장 빠름

- NVME 프로토콜을 채용한 드라이버를 사용하여 m.2 커넥터의 PCIe 버스에 연결된 SSD를 사용한다.

- 예) 삼성 970 EVO M.2 2282 SSD (x4 레인용)

- 예) 킹스톤 A1000 M.2 2280 (x2 레인용)

위에서 구분한 내용을 아래 그림을 보고 실제 제품 형태와 비교해보자.

- 주의할 것은M.2 key B+M 타입의 카드들은 외형만을 보고 SATA 버스를 사용하는 SSD인지 고속 PCIe 버스를 사용하는 SSD인지 구분할 수 없으므로 주의해야 한다.

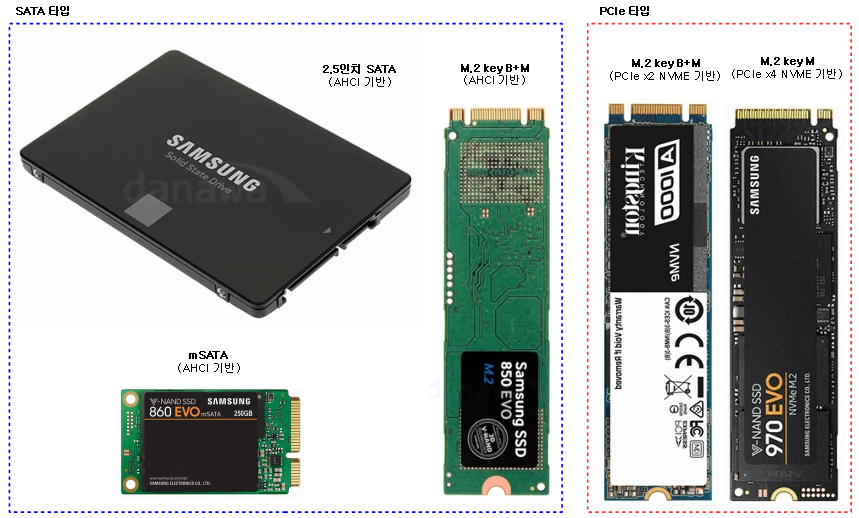

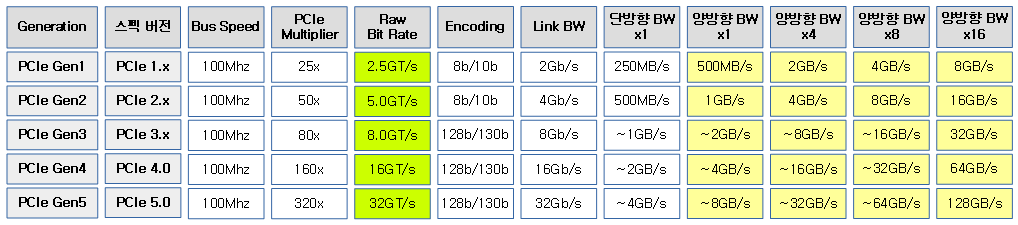

PCIe 버전

- 오늘날 가장 많이 사용되는 규격이다.

- 최근 임베디드 시스템에서 사용하는 PCI 규격이다.

PCIe 속도 비교

PCI Express 특징

- 저비용

- 저 비용으로 대량 양산 가능한 솔루션이다.

- 인터커넥트

- 커넥터나 케이블링을 통해 칩-to-칩 또는 보드-to-보드 연결 구성이 가능하다.

- 새로운 폼 팩터

- 모바일 및 모듈라 폼팩터 및 카트리지 폼팩터를 지원하는 새로운 폼 팩터이다.

- PCI 호환

- 기존 PCI 드라이버를 수정 없이 동작시킬 수 있는 호환성을 제공한다.

- 성능

- low-overhead, low-latency 통신을 통해 밴드폭과 링크 효과를 최대화한다.

- 최소한의 핀 수로 높은 밴드폭을 지원한다.

- lane들을 통합한 scalable 성능을 낼 수 있다.

- 향상된 기능

- 서로 다른 데이터 타입과 오더링 룰을 제공한다.

- 절전 관리

- 미니 PCI Express

- QoS

- 기존 핫플러그 및 native 핫플러그 지원 및 비동기 removal 지원한다.

- 모든 타입의 데이터에 대해 데이터 정합성(Data Integrity)을 제공한다.

- 진보된 에러 리포팅 및 에러 핸들링을 통해 향상된 폴트 isolation 및 리커버리 솔루션을 제공한다.

- 간편한 테스트 지원

PCIe 전송 H/W

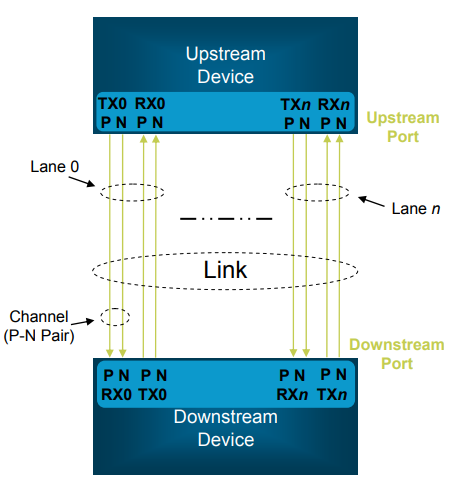

PCI Express 링크

패킷을 주고(Transmit) 받을(Receive) 수 있는 하나의 lane으로 PCI Express 링크를 구성할 수 있다. 또한 2 개 이상의 lane을 묶어(aggregation) 하나의 링크로 만들면 통신 속도를 통합한 lane 만큼 높일 수 있다.

- 1 개의 lane 부터 최대 32개의 lane을 하나 링크로 묶어 고속 통신이 가능하다.

- x1, x2, x4, x8, x12, x16, x32 lane을 지원한다.

- 1개의 lane에는 TX 페어와 RX 페어가 사용된다.

- 1개의 링크는 두 개의 디바이스끼리만 통신할 수 있다.

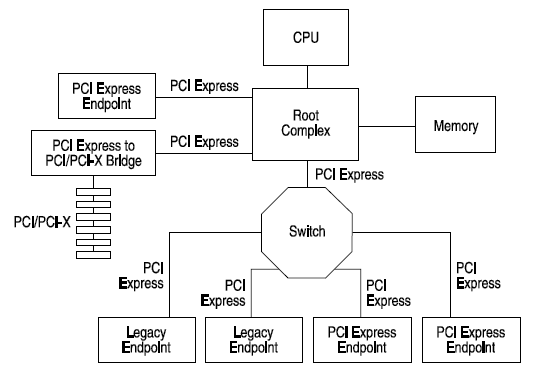

PCI Express Fabric Topology

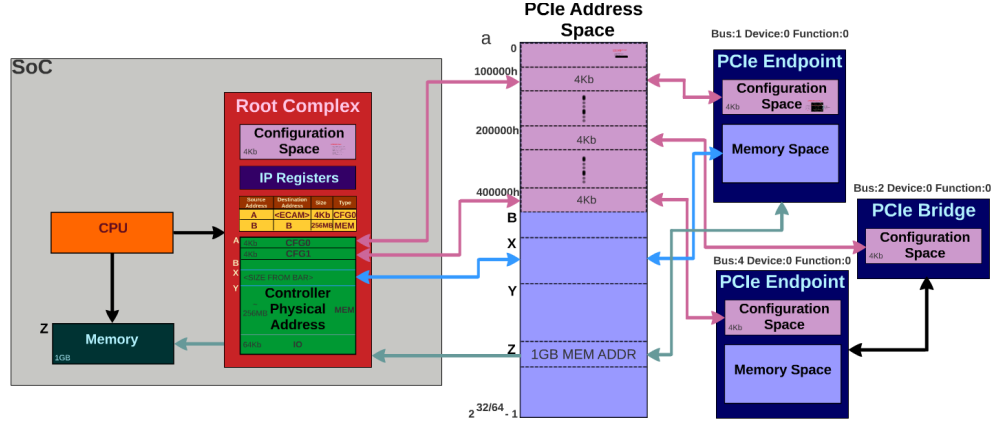

다음 그림에서 SoC가 Root Complex 가상 PCI Bridge를 통해 PCIe 버스를 3개 제공하는 것을 보여준다. 각각의 버스를 다음과 같이 사용하고 있다.

- BUS 1

- PCIe 버스를 브릿지를 통해 PCI 또는 PCIX 버스로 변환한다.

- BUS 3

- PCIe 버스에 PCI Express Switch를 연결하여 더 많은 PCIe 버스를 제공하기 위해 확장한다.

- BUS 9

- PCIe 버스에 하나의 디바이스만 곧장 연결하여 사용한다.

PCI 버스가 CPU와 연결되는 가장 상위는 Root Complex Device이고 버스를 확장하기 위해 PCI Switch를 사용할 수 있다.

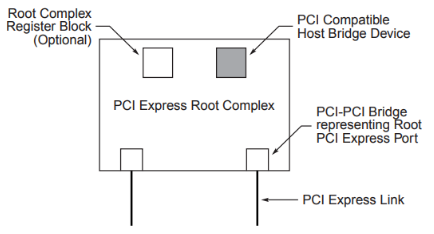

1) Root Complex 디바이스

루트 컴플렉스(RC)는 CPU/메모리 서브시스템을 I/O 연결할 수 있는 I/O 계층 구조의 루트이다.

- 루트 컴플렉스는 1개 이상의 PCI Express 포트를 가질 수 있다.

- PCI Express 포트는 하나의 End Point 디바이스와 연결되거나, 브리지나 스위치를 통해 확장할 수 있다.

- 구현 옵션에 따라 peer-to-peer 트랜잭션 전송이 가능하다.

- 드물지만 디바이스별 페이로드 제한에 따라 하나의 패킷을 분할하여 전송하는 경우도 있다.

PCI Express 루트 컴플렉스 디바이스를 더 자세히 살펴보면 다수의 내부 PCI-PCI 브리지 구조로 구성된다.

- 호스트 브릿지 디바이스

- 호스트에 연결된다.

- 루트 PCI Express 포트

- 하나의 PCI Expresss이다.

- 브리지의 세컨더리 버스에 해당하는 Configuration Space에 매핑된다.

2) Endpoint 디바이스

- Legacy PCI Endpoint

- Type 0 Configuration 헤더를 제공하는 Function이어야 한다.

- 반드시 Configuration을 제공해야 한다.

- I/O 요청을 제공할 수도 있다.

- I/O 요청을 발생시킬 수 있다.

- Locked 요청을 할 수 없다.

- MSI/MSI-X를 지원한다.

- 4G 주소를 초과하는 메모리 트랜잭션을 할 수 없다.

- 32비트 어드레싱 레지스터

- PCI Express Endpoint

- Type 0 Configuration Space를 제공하는 Function이어야한다.

- 반드시 Configuration을 제공해야 한다.

- I/O 요청을 발생시키면 안된다.

- Locked 요청을 지원하지 않는다.

- MSI/MSI-X를 지원한다.

- 4G 주소를 초과하는 메모리 트랜잭션이 가능하다.

- 64비트 어드레싱 레지스터

- 32비트 어드레싱도 가능하다.

- Root Complex Integrated Endpoint

- 루트 컴플렉스의 내부 로직에 구현된 루트 포트이다.

- Type 0 Configuration Space를 제공하는 Function이어야한다.

- 반드시 Configuration을 제공해야 한다.

- I/O 요청을 발생시키면 안된다.

- Locked 요청을 지원하지 않는다.

- MSI/MSI-X를 지원한다.

- 32비트 BAR를 통한 메모리 리소스를 지원한다.

- PCI Express Extended Capability를 구현하면 안된다.

- 전원 관리를 구현하지 않는다.

- 핫플러그를 지원하지 않는다. (당연하다.)

- 루트 컴플렉스가 노출하는 계층에 나타나면 안된다.

- 스위치에서도 나타나면 안된다.

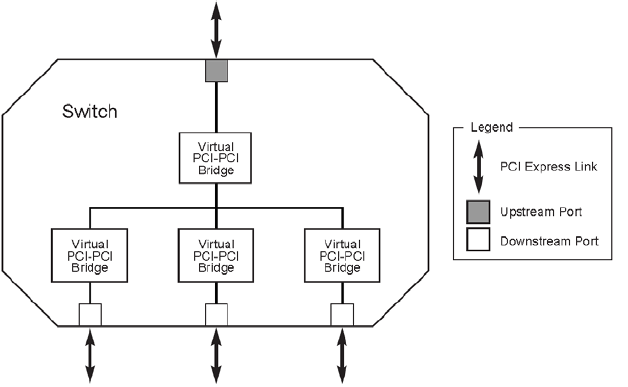

3) Switch 디바이스

스위치는 다 수의 가상 PCI-to-PCI 브리지 디바이스들로 내부적으로 구성되어 있다.

- 멀티캐스트를 제외한 트랜잭션을 라우팅 주소 기반으로 PCI 브리지 메커니즘을 사용하여 전달(forward)한다.

- 다운스트림 포트 방향으로 Locked 요청을 지원한다.

- 모든 활성화된 스위치 포트는 플로우 컨트롤을 지원할 수 있어야 한다.

- 패킷을 작은 사이즈로 분리하는 것을 지원하지 않는다.

- 인바운드된 포트 간에 중재는 라운드 로빈 또는 가중치 라운드 로빈을 구현할 수 있다.

- Endpoint는 스위치 내부 버스의 가상 PCI-to-PCI 브릿지의 피어로 노출되면 안된다.

- 하나의 업스트림 PCI Express 포트와 다수의 다운스트림 PCI Express 포트로 구성된다.

4) Root Complex Event Collector

- 메모리 및 IO 리소스를 디코딩할 필요가 없다.

- 다비이스/포트 타입 값으로 식별할 수 있다.

- 베이스 클래스(0x08), 서브 클래스(0x07)과 프로그래밍 인터페이스(0x00) 값을 사용한다.

- 싱글 로지컬 버스에 상주한다.

- 옵션으로 제공된다.

5) PCI Express to PCI/PCI-X Bridge

- PCI Express fabric과 PCI/PCI-X 계층간의 연결을 지원한다.

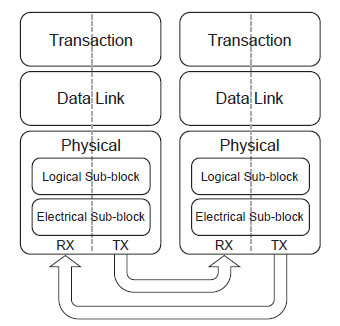

전송 계층

PCI 전송에 다음 3가지의 전송 계층을 사용한다.

- Transaction Layer

- Data Link Layer

- Physical Layer

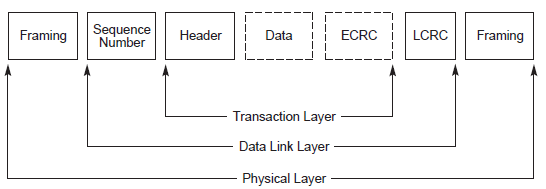

3 계층의 TLP(Transaction Layer Packet) 또는 2 계층의 DLLP(Data Link Layer Packet)을 전송하며 각 계층에서 취급하는 데이터는 다음과 같다.

TLP(Transaction Layer Packet)

- Physical Layer

- Framing

- Start (1B)

- End (1B)

- Framing

- Data Link Layer

- Sequence Number (2B)

- LCRC (1DW)

- Transaction Layer

- Header (3~4DW)

- Data (0~1024DW)

- ECRC (1DW)

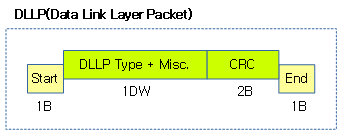

DLLP(Data Link Layer Packet)

- Physical Layer

- Framing

- Start (1B)

- End (1B)

- Framing

- Data Link Layer

- DLLP Type + Misc (1DW)

- CRC (2B)

Transaction Layer

- TLPs(Transaction Layer Packets)의 생성과 처리

- 메모리 트랜잭션

- Memory 주소 공간에 매핑

- I/O 트랜잭션

- I/O 주소 공간에 매핑

- Configuration 트랜잭션

- 디바이스 펑션 설정 및 셋업

- 메시지 트랜잭션

- 이벤트 시그널링에서 일반적인 메시징까지

- 메모리 트랜잭션

- 플로우 컨트롤

- 가상 채널 관리

- PCI/PCI-X 호환 오더링

- 트래픽 클래스 differentiation 포함

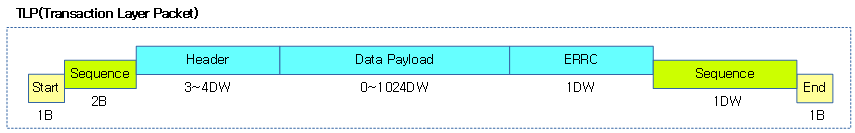

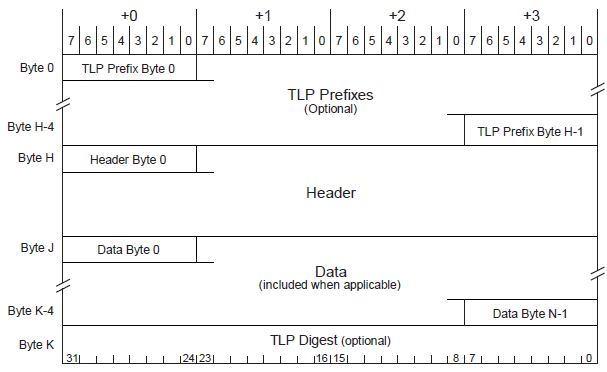

TLPs(Transaction Layer Packets) Header 포맷

트랜잭션 레이어 패킷은 다음과 같은 구성을 사용한다. 전송 시 Byte 0 위치부터 시작한다.

- TLP Prefixes (optional)

- TLP Header

- Data Payload

- TLP Digest (optional)

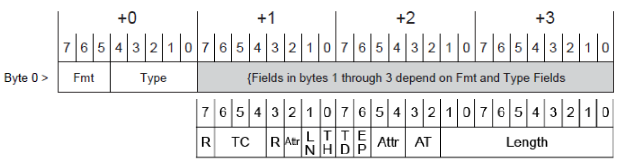

TLP 헤더

다음 그림은 TLP 헤더와 패킷 포맷을 보여준다. 패킷 포맷에 따라 1~4바이트의 TLP 헤더를 갖는다.

- 아래 그림에 이어 32비트 주소 또는 64비트 주소가 추가된 주소 라우팅을 표시한다.

- 32비트 주소 라우팅의 경우 3 DW 헤더 길이를 갖는다.

- 64비트 주소 라우팅의 경우 4 DW 헤더 길이를 갖는다.

- Fmt

- 패킷 포맷

- Type

- 패킷 타입

- R

- Reserved로 반드시 0 이어야 한다.

- TC

- 트래픽 클래스로 QoS 목적으로 사용한다.

- 000: TC0로 가장 우선 순위가 느린 베스트 Effort 처리 방식이다.

- 001 ~ 111: TC1 ~ TC7으로 스케줄러를 통해 처리 순서를 제어할 수 있다.

- 트래픽 클래스로 QoS 목적으로 사용한다.

- Attr

- 속성

- LN

- 메모리 요청이 LN Read, LN Write 이거나,

- 컴플리션이 LN Completion인 경우이다.

- TH

- TLP 처리 힌트를 의미한다.

- TD

- TLP 다이제스트를 의미한다.

- EP

- poisned TLP를 의미한다.

- Attr

- 오더링 타입을 표시하는 속성이다.

- Attr[2:1]

- 00: 디폴트 오더링

- PCI Strongly 오더드 모델이다.

- 01: 릴렉스드 오더링

- PCI-X 릴렉스드 오더링 모델이다.

- 10: ID 베이스 오더링

- 리퀘스터와 컴플리터 ID 기반의 독립적인 오더링이다.

- 11: 릴렉스드 오더링 + ID 베이스 오더링

- 00: 디폴트 오더링

- Attr[0]

- 0: 디폴트

- 하드웨어가 수행하는 캐시 코히런시

- 1: No Snoop

- 하드웨어가 캐시 코히런시를 수행하지 않는다.

- 0: 디폴트

- AT

- 주소 타입으로 주소 변환이 필요한지 여부를 의미한다.

- 00: 디폴트로 변환하지 않는다.

- 01: 변환 요청

- 10: 변환됨

- 11: Reserved

- Length

- DW(4바이트, 더블 워드) 단위의 데이터 페이로드 길이

- 0~1023까지 지정이 가능하다. 단 0의 경우 1024 DW를 의미한다.

- 트랜스미터(Transmiter) 또는 리시버(Receiver) 디바이스 컨트롤 레지스터의 Max_Payload_Size 필드(DW 단위)를 초과하면 안된다.

패킷 포맷

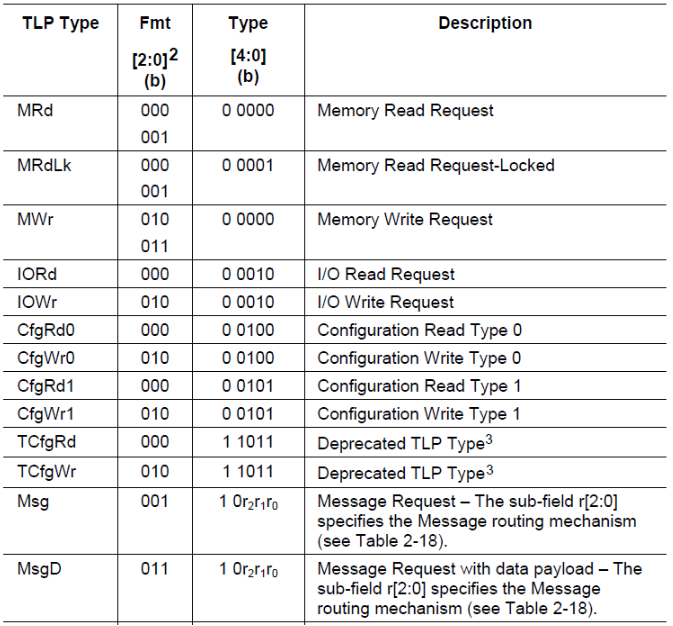

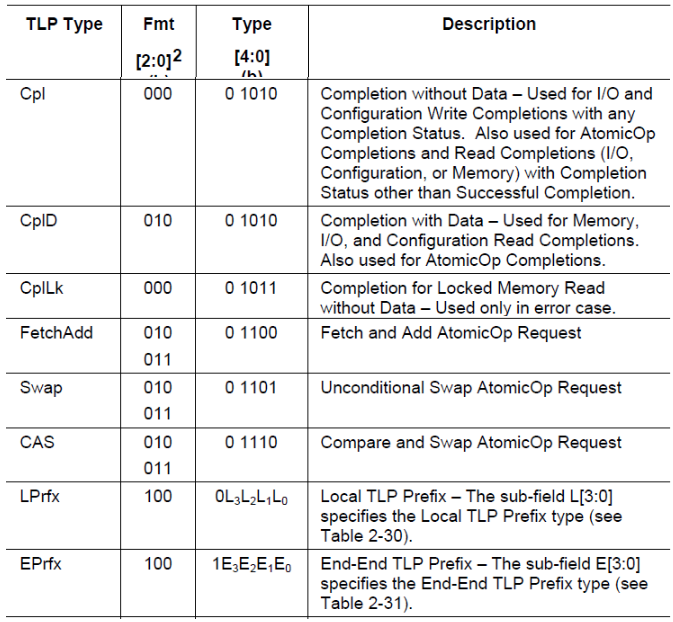

TLP 타입

다음 표에서 트랜잭션 타입을 보여준다.

트랜잭션 처리 방향

Non-Posted (응답 확인 필요)

- Memory Reads.

- MRd 요청: 디바이스가 Root Complex에 메모리 읽기 요청

- CplD 응답: Root Complex에 연결된 시스템 메모리를 읽어 디바이스에 Completion 데이터 응답

- Memory Locked Reads

- MRdLk 요청: Root Complex가 락을 유지한채 디바이스에 메모리 읽기 요청

- CplDLk 응답: 디바이스가 Completion 데이터 응답

- IO 및 Configuration Writes

- IOWr 요청: Root Complex가 디바이스에 IO 쓰기 요청

- Cpl 응답: 디바이스가 데이터를 기록한 후 Completion 응답

Posted (응답 확인 없음)

- Memory Writes

- MWr 요청: Root Complex가 디바이스에 메모리 기록 요청한다. 그 후 응답은 받지 않는다.

- Message Writes

- Msg 요청: 트랜잭션 메시지 라우팅

트랜잭션 라우팅

다음과 같이 두 가지 타입의 라우팅이 지원된다.

- 주소 라우팅

- 64비트 주소 라우팅

- 32비트 주소 라우팅

- ID 라우팅

- non-ARI ID 라우팅

- ARI ID 라우팅

64/32 비트 주소 라우팅

- PH

- 00: 양방향 데이터

- 01: 요청자

- 10: 타겟

- 11: 우선순위 포함한 타겟

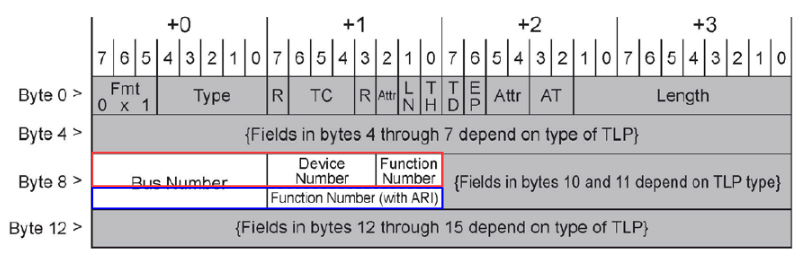

ID 라우팅

- non ARI ID 라우팅

- Bus 번호, 디바이스 번호 및 펑션 번호 세 가지를 사용한다.

- ARI ID 라우팅

- Bus 번호 및 펑션 번호 두 가지를 사용한다.

아래 그림은 4 DW 길이의 TLP 헤더이다. 포맷이 0 x 0 인 경우 3 DW 길이의 TLP 헤더를 사용한다.

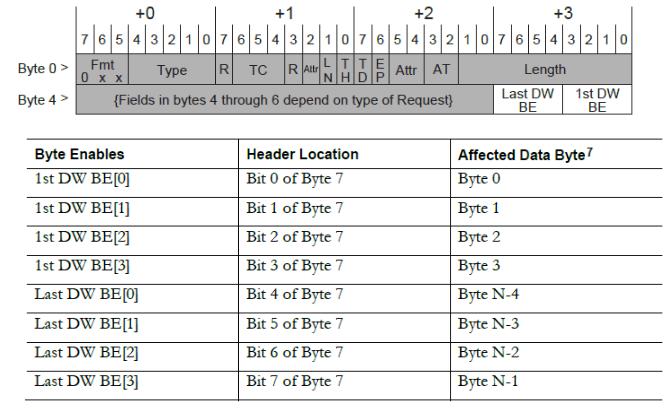

First/Last DW Byte Enables

TH 비트가 설정된 메모리 읽기 요청은 다음표와 같이 첫번째와 마지막 DW에 대한 바이트 enable을 표시한다.

Request (메모리, I/O, Configuration)

Request Memory

다음 그림은 메모리, I/O 및 Configuration 트랜잭션 데이터를 요청할 때 사용하는 TLP 헤더이다. (Memory 32비트는 생략)

Data Link Layer

- 링크 트레이닝

- 링크 폭

- 링크 데이터 rate

- Lane reversal (Lane 역 방향 순서 지원)

- Polarity inversion (극성 반대 지원)

- 멀티 레인에서 레인 to 레인 de‐skew

- 전원 관리

- 트랜잭션 게층에서 요청한 전원 상태를 수락하고 물리 계층으로 전달한다.

- 활성/재설정/연결 해제/전원 관리 상태를 트랜잭션 계층으로 전달한다.

- 데이터 프로텍션, 에러 체킹

- CRC 생성

- 에러 체킹

- 재전송 메시리지대한 TLP 응답

- 에러 리포팅 및 로깅을 위한 에러 인디케이션

Physical Layer

- 인터페이스 초기화, 메인트넌스 제어 및 스테이터스 트래킹

- 리셋/핫플러그 컨트롤

- 전원 관리 인터커넥트

- width & lane 매핑 협상

- lane 극성 반전

- 심볼 및 오더

- 8b/10b 엔코딩 및 디코딩

- 임베디드 클럭 튜닝 및 정렬

- 심볼 전송 및 정렬

- 전송 회로

- 리셉션 회로

- 수신 측 Elastic 버퍼

- 수신 측 멀티 lane de-skew

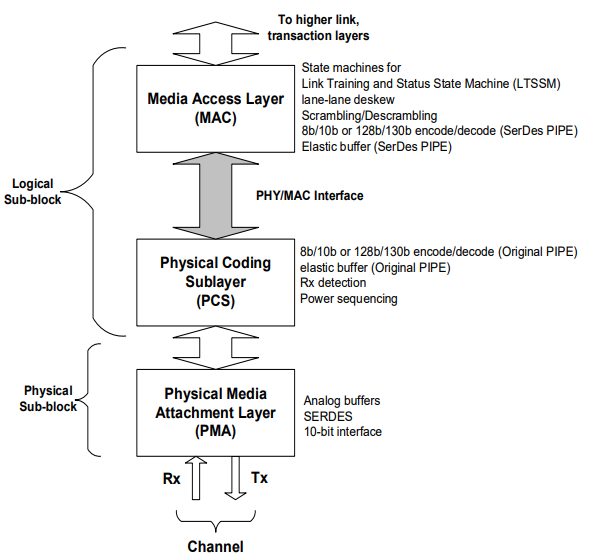

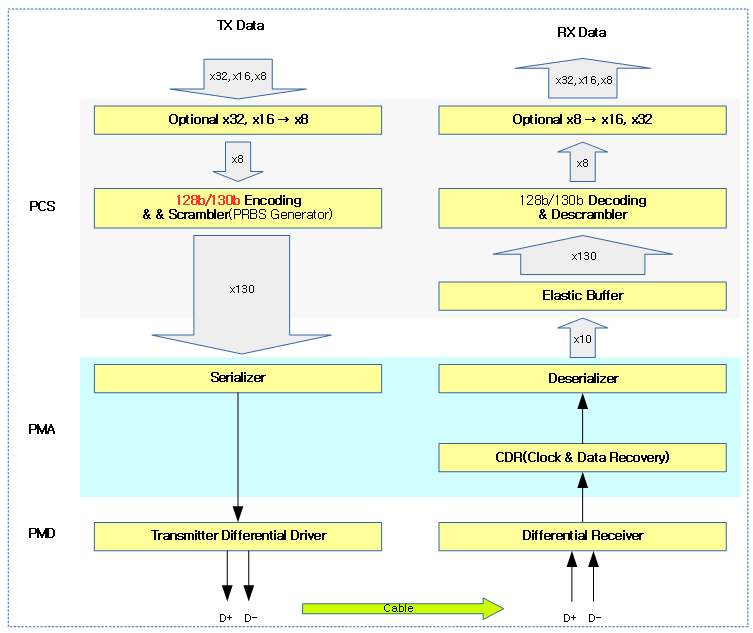

MAC & PHY 인터페이스

데이터 전송 계층의 MAC과 물리 계층의 PHY간의 인터커넥트

- MAC

- 링크 관리

- PHY

- PCS(Physical Coding Sublayer)

- 코드 변환을 수행한다.

- PMA(Physical Medium Attachment)

- 물리 매체 접속부로 Serialization/Deserialization 기능을 수행한다.

- 수신부(Receiver)에는 클럭 및 데이터의 리커버리 기능도 포함된다.

- PMD(Physical Medium Dependent Sublayer)

- 물리 매체 전송부로 전송 매체에 최적화된 트랜시버 모듈(광 트랜시버 등)

- PCS(Physical Coding Sublayer)

PCS & PMA & PMD

물리 전송 계층의 3가지 서브 레이어를 각 기능별로 송/수신 흐름을 알아본다.

PCIe Gen1 & Gen2

PCIe Gen3 & Gen4 & Gen5

Encoding

다음과 같은 엔코딩을 사용하여 5개 이상의 비트가 연속되지 않게 제한시킨다. 이렇게 하므로써 출력이 커지는 것을 방지하여 EMI 방사(radiation)를 줄여준다.

- 8b/10b

- PCIe Gen 1과 Gen 2에서 사용한다.

- 8비트 입력에 대해 2비트가 추가되어 10비트가 출력된다.

- 25%의 추가 대역폭이 필요하다.

- 예) 1Gbps -> 1.25Gbps

- 25%의 추가 대역폭이 필요하다.

- 128b/130b

- PCIe Gen3 이후부터 사용한다.

- 128비트 입력에 대해 2비트가 추가되어 130비트가 출력된다.

- 소모되는 추가 대역폭이 1% 미만으로 거의 없다.

Configuration Topology

PCI Express Configuration 모델은 두 개의 Configuration Space access 매커니즘을 지원한다.

- PCI compatible CAM(Configuration Access Mechanism)

- 호환을 위해 PCI express 디바이스는 이 항목을 항상 제공한다.

- PCI Express ECAM(Enhanced Configuration Access Mechanism)

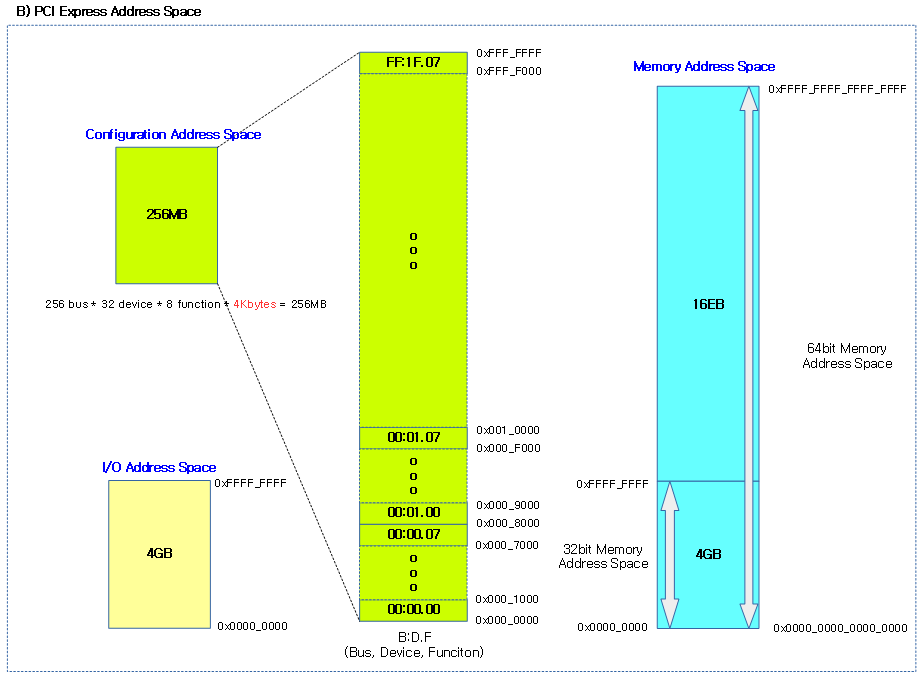

PCI Express Address Space

PCI Express는 PCI와 유사하지만 다음과 같은 변화가 있다.

- Configuration Address space의 크기가 256 바이트에서 4K 바이트로 확장되었다.

- Memory Address space는 32비트와 64비트 두 가지 방법으로 주소 지정할 수 있다.

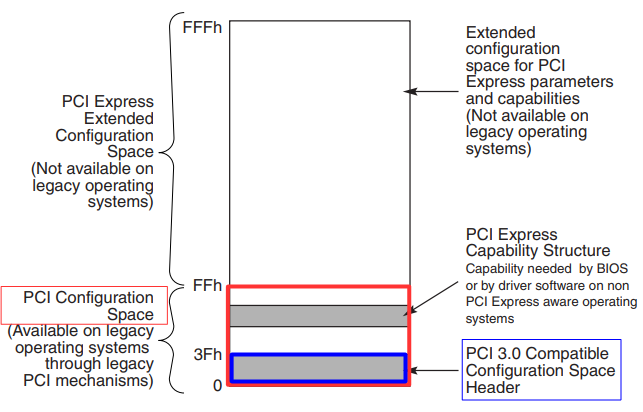

PCI Express Configuration Space Layout

PCI Express 하나를 담당하는 Configuration Space를 알아본다.

- PCI 호환 주소 영역

- 0x00 ~ 0xff의 영역을 갖는다.

- 그 중 헤더 영역은 0x00 ~ 0x3f이다.

- PCI Express 확장 주소 영역

- 0x100 ~ 0xfff의 영역을 갖는다.

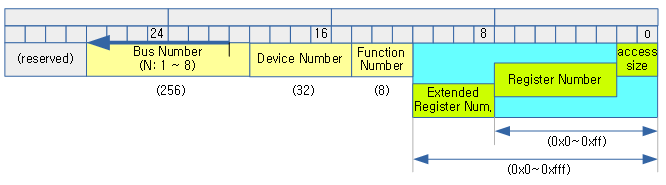

ECAM(Enhanced Configuration Access Mechanism)

다수의 PCI Express 버스를 관리하기 위해 아래와 같은 주소 체제로 나누어 사용한다.

- 버스 번호

- 1부터 최대 256개의 버스 번호를 가질 수 있다.

- 디바이스 번호

- 최대 32개의 디바이스 번호를 가질 수 있다.

- 펑션 번호

- 최대 8개의 펑션 번호를 가질 수 있다.

- PCI Express Configuration Space

- 0x0 ~ 0xfff까지의 영역을 담당한다.

다음 그림은 Root Complex 가상 PCI Bridge가 3개의 PCIe 버스를 제공하며 이에 대한 pci 주소 공간을 보여준다.

- Root Complex에 해당하는 configuration space가 주어진다.

- 그 아래에 각 가상 PCI Bridge에 해당하는 configuration space가 있음을 알 수 있다.

Configuration Space Header

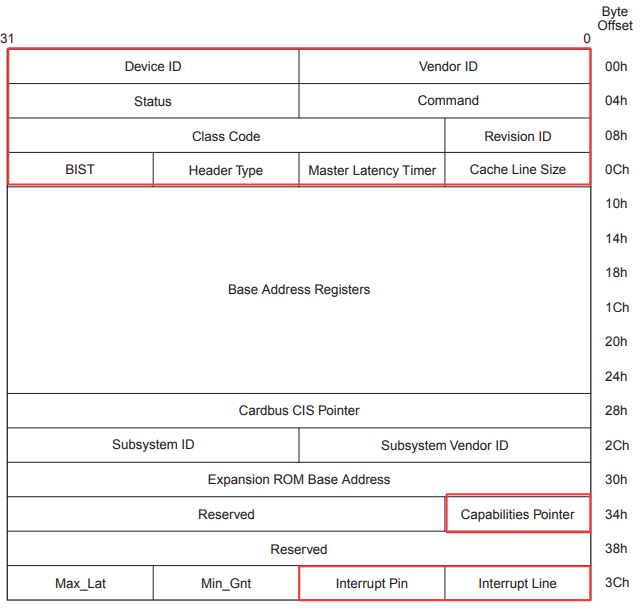

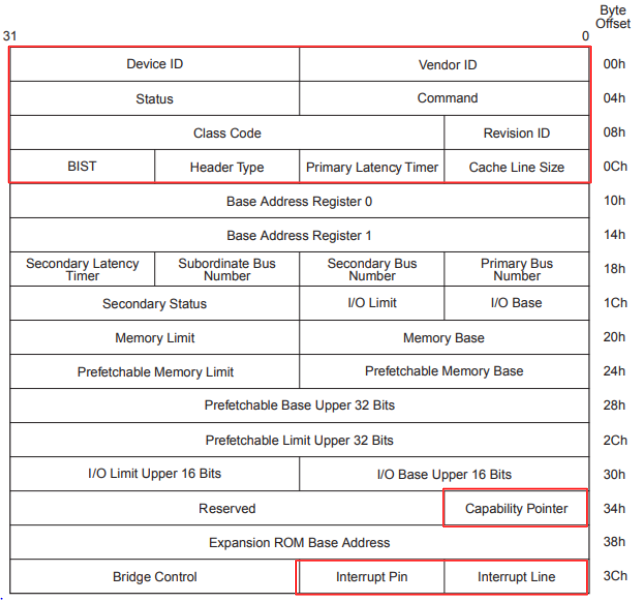

디바이스 타입에 따라 Configuration Space Header는 다음과 같이 2 가지 타입을 지원한다.

- Type 0 header

- PCI Express 디바이스

- Type 1 header

- Switch 및 Root Complex 가상 PCI Bridges

Type 0 헤더

Type 1 헤더

각 헤더에서 사용되는 공통 레지스터들

Vendor ID (0x00)

- 2바이트 벤더 ID

- 예) 인텔: 0x8086

Device ID (0x02)

- 2바이트 디바이스 ID

- 예) 고속 이더넷 장치: 0x0009

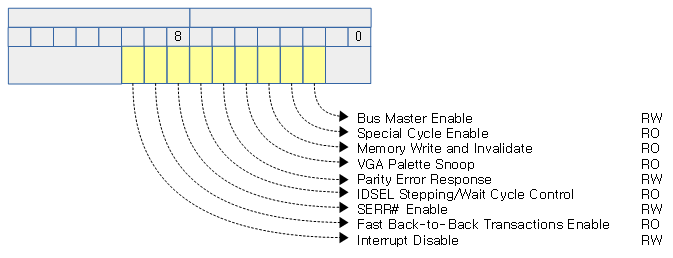

Command (0x04)

- 2바이트 명령 레지스터

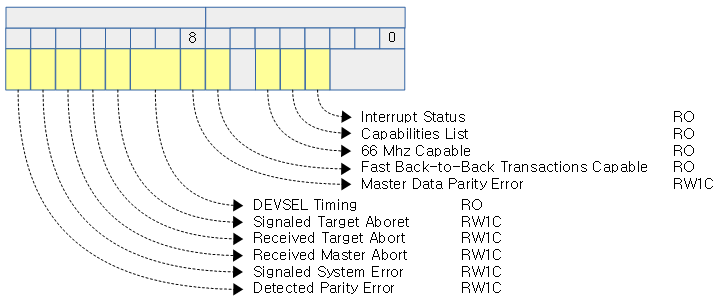

Status (0x06)

- 2 바이트 상태 레지스터

- RW1C (Read, Write 1 to Clear Status)

- Read는 동일하되, 1 값을 기록 시에만 클리어한다. 0을 기록시에는 아무런 변화가 없다.

Revision ID (0x08)

- 1 바이트 Revision ID

Class Code (0x09)

- 3 바이트 클래스 코드로 장치 유형을 표시한다.

- 예) SCSI: 0x0100

Cache Line Size (0x0c)

- 1바이트 캐시 라인 사이즈

- 호환 목적으로 사용되며 PCI express에서는 사용하지 않으므로 항상 0이다.

Primary Latency Timer (0x0d)

- 1바이트 대표 Latency 타이머

- PCI express에서는 사용하지 않으므로 항상 0이어야 한다.

Header Type

- 1바이트 헤더 타입

BIST

- 1바이트 BIST

Interrupt Line (0x3c)

- 1 바이트 인터럽트 번호로 디바이스 드라이버에서 사용하는 정보이다.

Interrupt Pin (0x3d)

- 1 바이트 실제 라우팅되는 legacy 인터럽트 라인 번호로 1~4까지 (INTA, INTB, INTC, INTD) 주어질 수 있다. 0인 경우 사용하지 않는다.

Type 0 레지스터들

BAR(Base Address Register) (0x10~0x24)

- 6개의 BAR를 제공한다.

- PCI I/O, PCI 메모리 공간의 유형과 크기, 위치를 지정하는데 사용된다.

Min_Gnt (0x3e)

- 1 바이트로 PCI Express에서는 사용되지 않고, 0으로 고정되어 있다.

Max_Lat (0x3f)

- 바이트로 PCI Express에서는 사용되지 않고, 0으로 고정되어 있다.

Type 1 레지스터들

BAR(Base Address Register) (0x10~0x24)

- 2개의 BAR를 제공한다.

Primary Bus Number (0x18)

- 1 바이트로 PCI Express에서는 사용되지 않는다.

Secondary Bus Number (0x19)

- 1 바이트

Subordinate Bus Number (0x1a)

- 1 바이트

Secondary Latency Timer (0x1b)

- 1 바이트로 PCI Express에서는 사용되지 않고, 0으로 고정되어 있다.

I/O Base (0x1c)

I/O Limit (0x1d)

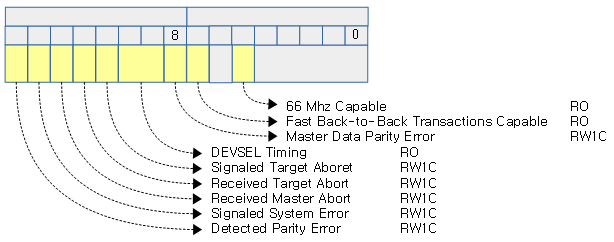

Secondary Status Register (0x1e)

- 2 바이트 두 번째 상태 레지스터

Prefetchable Memory Base

- 전체 64비트로 PCI Bridge에서 사용된다.

Prefetchable Memory Limit

- 전체 64비트로 PCI Bridge에서 사용된다.

Capability Pointer (0x34)

- 1 바이트로 Capability가 있는 경우 첫 Capability offset이 기록되어 있다.

Expansion ROM Base Address (0x38)

- 4 바이트

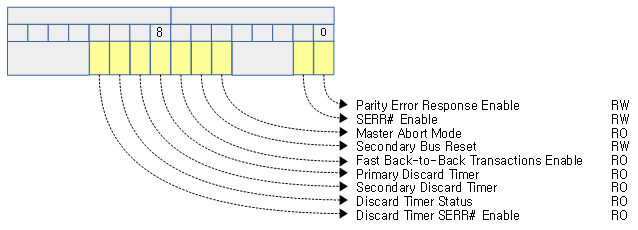

Bridge Control (0x3e)

- 2 바이트로 PCI Bridge에서 사용된다.

참고

- PCI Subsystem -1- (Basic) | 문c – 현재글

- PCI Subsystem -2- (Core) | 문c

- PCI Subsystem -3- (Host Controller) | 문c

- How To Write Linux PCI Drivers | Kernel.org

- PCIe driver development for Exynos SoC | 삼성 한진구 – 다운로드 pdf

- Linux PCI drivers | Free Eletrons – 다운로드 pdf

- Overview of the PCI Specification – 다운로드 ppt

- Overview of PCI subsystem | Kishon Vijay Abrahma I, Vignesh R – 다운로드 pdf

- PCI Express® Base Specification Revision 4.0 Version 0.3 – 다운로드 pdf

- PCI Drivers | KLDP-Wiki

자세히 작성 공유해 주신 글 잘 읽고 갑니다. ^^ 고맙습니다.

감사합니다. ^^

큰 도움이 되었습니다.

항상 잘 배우고 있습니다.

감사합니다.

소중한 격려에 감사드립니다. 좋은 하루 되세요.