<kernel v5.10>

ARM64 페이지 테이블 -2- (매핑)

ARM64 커널 메모리 맵

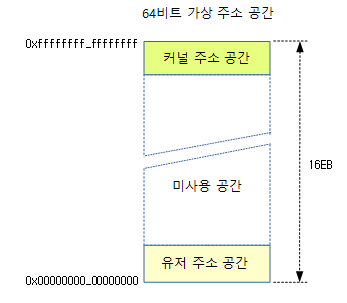

ARM64 커널에서 커널용 가상 주소 영역을 좀 더 자세히 알아보면, 그 영역의 절반을 잘라서 2개로 나누어 이용한다. 하위 절반은 물리 메모리를 1:1로 미리 리니어 매핑하여 사용하고, 나머지 상위 절반은 fixmap, vmalloc, vmemmap, pci-iomap 영역 및 커널 이미지 영역으로 나누어 사용한다.

그중에서 fixmap과 vmalloc 영역 동적으로 매핑하여 사용할 수 있는 공간으로 사용한다. 커널 주소 공간을 제외한 그 외 매핑 영역별 용도는 다음과 같다.

- fixmap: 컴파일 타임에 목적에 따라 가상 주소 공간이 이미 결정된 매핑 영역이다.

- vmalloc: 런타임에 연속된 가상 주소 공간을 자유롭게 매핑할 수 있는 영역이다.

- vmalloc( ) 함수가 vmap( ) 함수를 통해 이용하는 곳이고, ioremap( ) 함수 역시 사용하는 영역이다.

- pci-iomap: PCI 디바이스의 메모리 맵 I/O 영역으로 사용하는 영역이다. pci-ioremap 영역은 PCI 디바이스만 사용하는 데 반해 일반 ioremap 함수를 통해 매핑하는 곳은 vmalloc 영역임을 주의해야 한다.

- vmemmap: 빠른 접근을 위해 분산된 page 구조체들을 이 영역에 매핑하기 위해 사용한다.

페이징 초기화

페이징에 사용하는 커널용 페이지 테이블을 초기화한다. 아직 커널 메모리 영역이 매핑되지 않은 상태이므로 memblock을 사용하여 페이지를 할당받아도 이에 해당하는 가상 주소가 없으므로 곧바로 할당받은 페이지에 접근할 수 없다. 커널의 부트업 과정 초반에는 이렇게 메모리 관리 및 매핑 관리가 동작하기 전 상태이므로 고정 매핑(fixmap) 주소 공간을 활용한 early 매핑에 대한 방법도 제공한다. 이 과정이 완료되면 정규 메모리 할당은 아직 동작하지 않지만, memblock을 이용한 early 메모리 할당이 가능해진다.

paging_init() – ARM64

arch/arm64/mm/mmu.c

/*

* paging_init() sets up the page tables, initialises the zone memory

* maps and sets up the zero page.

*/

void __init paging_init(void)

{

pgd_t *pgdp = pgd_set_fixmap(__pa_symbol(swapper_pg_dir));

map_kernel(pgdp);

map_mem(pgdp);

pgd_clear_fixmap();

cpu_replace_ttbr1(lm_alias(swapper_pg_dir));

init_mm.pgd = swapper_pg_dir;

memblock_free(__pa_symbol(init_pg_dir),

__pa_symbol(init_pg_end) - __pa_symbol(init_pg_dir));

memblock_allow_resize();

}

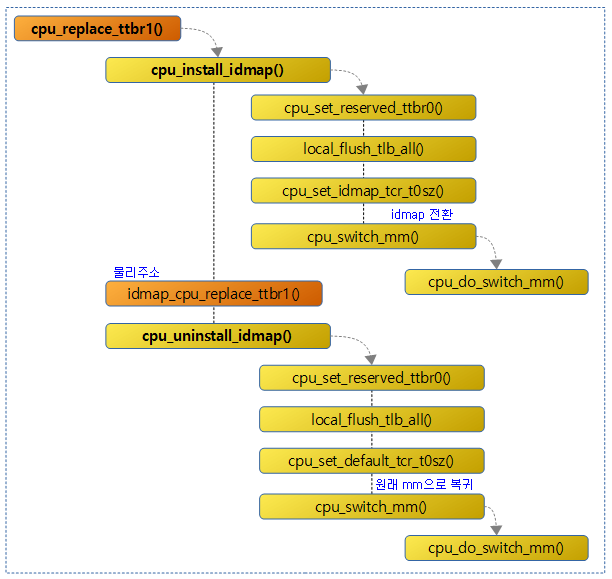

커널 부트업 과정에서 커널 이미지를 모두 RW가 가능한 페이지 테이블인 init_pg_dir을 사용하여왔다. 이를 버리고 커널 코드 등이 read only등이 가능한 정규 커널 페이지 테이블인 swapper_pg_dir 체제로 변경한다. 즉 커널 코드 및 데이터 영역, DRAM 영역을 커널용 페이지 테이블을 가리키는 swapper_pg_dir에 새롭게 매핑하고 메모리를 관리하기 위한 메모리 맵(mem_map)을 구성한다. 그런 후 swapper_pg_dir 페이지 테이블 체제를 활성화시킨다.

- 코드 라인 3에서 커널 페이지 테이블로 사용할 pgd 테이블로 컴파일 타임에 static하게 생성한 swapper_pg_dir 테이블을 사용하여 fixmap 영역의 pgd 엔트리에 매핑한다. fixmap에 매핑 하였으므로 swapper_pg_dir 페이지 테이블에 access가 가능해졋다.

- 어셈블리(head.S)로 구동된 커널 부트업을 통해 init_pg_dir 페이지 테이블에 커널을 임시 매핑하여 사용하고 있는 중이다.

- 임시로 사용 중인 init_pg_dir 페이지 테이블을 버리고 정식으로 swapper_pg_dir 페이지 테이블로 변경할 예정이다.

- 코드 라인 5~6에서 새로 사용할 swapper_pg_dir 페이지 테이블에 커널(코드 및 데이터) 영역과 메모리 영역을 매핑한다.

- 코드 라인 8에서 fixmap에 매핑한 swapper_pg_dir은 곧 ttbr 레지스터를 통해 정식으로 사용될 예정이므로 fixmap에서 분리하기 위해 fixmap 영역의 pgd 엔트리에 매핑한 pgd 테이블을 매핑 해제한다.

- 코드 라인 10~11에서 커널용 페이지 테이블을 가리키는 ttbr1이 새로 준비한 swapper_pg_dir을 가리키도록 한다.

- 코드 라인 13~14에서 임시로 사용한 init_pg_dir 페이지 테이블 영역을 memblock에 할당 해제 한다. (소멸)

- 코드 라인 16에서 지금부터 memblock이 확장될 수 있게 설정한다.

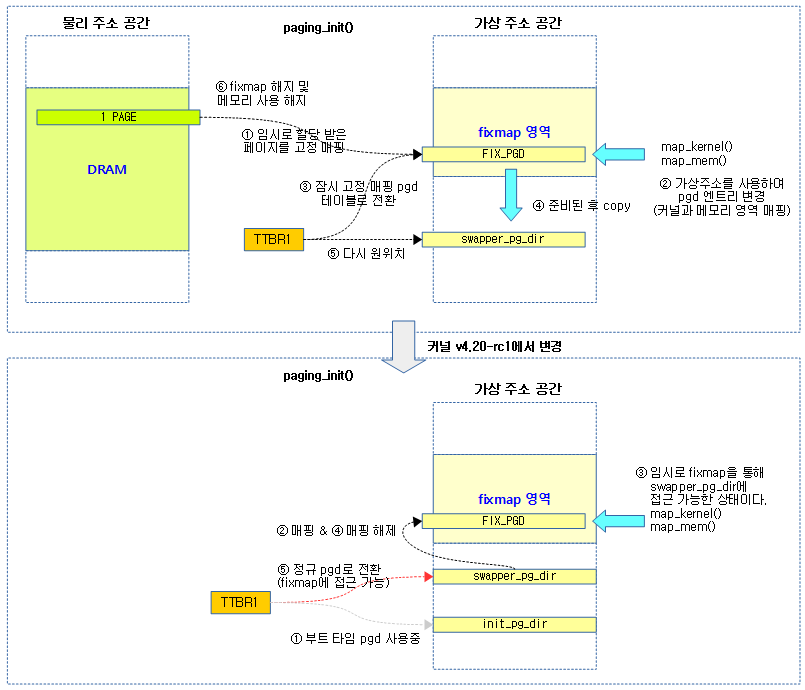

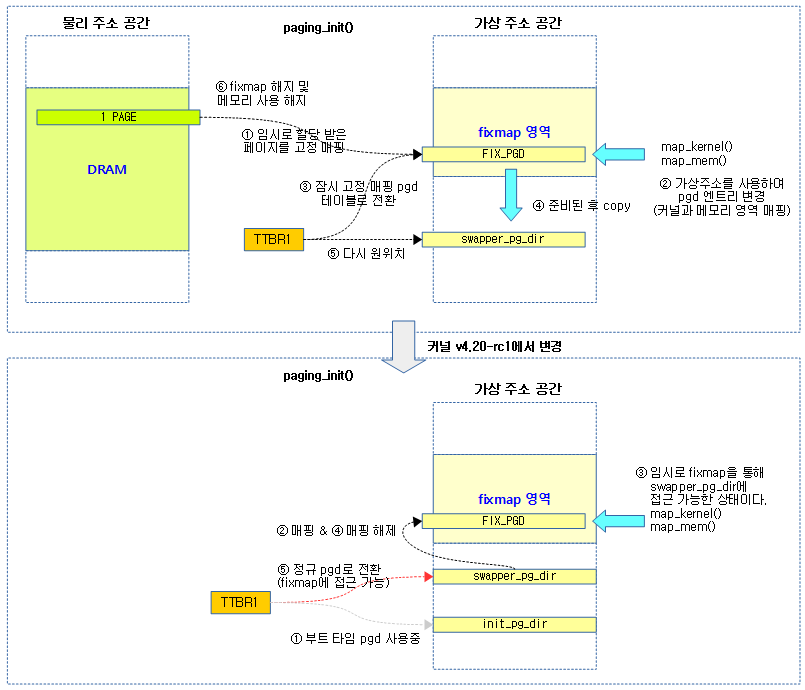

다음 그림은 커널이 부트 타임 pgd를 사용하다 fixmap을 이용하여 커널과 메모리를 매핑 후 정규 pgd로 전환하는 과정이다.

- v4.20-rc1에서 부트 타임 pgd인 init_pg_dir이 추가되면서 매핑 로직이 약간 변경되었다.

커널 매핑

map_kernel()

arch/arm64/mm/mmu.c

/*

* Create fine-grained mappings for the kernel.

*/

static void __init map_kernel(pgd_t *pgdp)

{

static struct vm_struct vmlinux_text, vmlinux_rodata, vmlinux_inittext,

vmlinux_initdata, vmlinux_data;

/*

* External debuggers may need to write directly to the text

* mapping to install SW breakpoints. Allow this (only) when

* explicitly requested with rodata=off.

*/

pgprot_t text_prot = rodata_enabled ? PAGE_KERNEL_ROX : PAGE_KERNEL_EXEC;

/*

* If we have a CPU that supports BTI and a kernel built for

* BTI then mark the kernel executable text as guarded pages

* now so we don't have to rewrite the page tables later.

*/

if (arm64_early_this_cpu_has_bti())

text_prot = __pgprot_modify(text_prot, PTE_GP, PTE_GP);

/*

* Only rodata will be remapped with different permissions later on,

* all other segments are allowed to use contiguous mappings.

*/

map_kernel_segment(pgdp, _text, _etext, text_prot, &vmlinux_text, 0,

VM_NO_GUARD);

map_kernel_segment(pgdp, __start_rodata, __inittext_begin, PAGE_KERNEL,

&vmlinux_rodata, NO_CONT_MAPPINGS, VM_NO_GUARD);

map_kernel_segment(pgdp, __inittext_begin, __inittext_end, text_prot,

&vmlinux_inittext, 0, VM_NO_GUARD);

map_kernel_segment(pgdp, __initdata_begin, __initdata_end, PAGE_KERNEL,

&vmlinux_initdata, 0, VM_NO_GUARD);

map_kernel_segment(pgdp, _data, _end, PAGE_KERNEL, &vmlinux_data, 0, 0);

if (!READ_ONCE(pgd_val(*pgd_offset_pgd(pgdp, FIXADDR_START)))) {

/*

* The fixmap falls in a separate pgd to the kernel, and doesn't

* live in the carveout for the swapper_pg_dir. We can simply

* re-use the existing dir for the fixmap.

*/

set_pgd(pgd_offset_pgd(pgdp, FIXADDR_START),

READ_ONCE(*pgd_offset_k(FIXADDR_START)));

} else if (CONFIG_PGTABLE_LEVELS > 3) {

pgd_t *bm_pgdp;

p4d_t *bm_p4dp;

pud_t *bm_pudp;

/*

* The fixmap shares its top level pgd entry with the kernel

* mapping. This can really only occur when we are running

* with 16k/4 levels, so we can simply reuse the pud level

* entry instead.

*/

BUG_ON(!IS_ENABLED(CONFIG_ARM64_16K_PAGES));

bm_pgdp = pgd_offset_pgd(pgdp, FIXADDR_START);

bm_p4dp = p4d_offset(bm_pgdp, FIXADDR_START);

bm_pudp = pud_set_fixmap_offset(bm_p4dp, FIXADDR_START);

pud_populate(&init_mm, bm_pudp, lm_alias(bm_pmd));

pud_clear_fixmap();

} else {

BUG();

}

kasan_copy_shadow(pgdp);

}

커널 코드를 의도하지 않은 수정으로부터 보호하고 실행 영역과 비실행 영역 또한 보호하기 위해 커널 코드와 데이터의 읽기 전용 영역과 읽고 쓰기 영역을 나누어 각각의 적절한 매핑 속성으로 매핑한다. 매핑할 페이지 테이블은 요청한 pgd 테이블의 포인터 @pgdp 이며, 이곳에 매핑을 수행한다.

- 코드 라인 11에서 커널 코드의 매핑 속성을 RW 또는 Read only(디폴트) 둘 중하나로 선택한다.

- external 디버거를 사용 시 sw 브레이크 포인터를 사용하여 커널 코드가 매핑된 영역에 직접 기록할 수 있다. 이러한 경우 커멘드라인 커널 파라메터에 “rodata=off”를 사용하여야 커널 영역을 read only로 하지 않고 기록도 가능하게 매핑할 수 있다.

- 코드 라인 18~19에서 cpu가 BTI(byte top ignore) 기능을 지원하는 경우 커널 코드의 매핑 속성에 PTE_GP 플래그를 추가한다.

- 코드 라인 25~26에서 커널 이미지의 일반 코드 영역을 커널 실행 페이지 타입으로 매핑한다.

- arm64 예) 메모리가 0x4000_0000에 위치한 커널 이미지에 대해 0x8_0000 offset만큼 떨어진 커널 코드를 커널용 가상 주소 중 kimage 영역에 매핑한다.

- phys=0x4008_0000, virt=0xffff_0000_1008_0000

- 코드 라인 27~28에서 커널 이미지의 읽기 전용 데이터 영역을 임시로 읽기 쓰기 가능한 커널 페이지 타입으로 매핑하되 contiguous 매핑을 하지 않도록 한다. rodata 섹션에 위치한 데이터들은 잠시 뒤 map_mem() 함수를 통해 PAGE_KERNEL 속성으로 재 매핑될 예정인데 contiguous 매핑 상태에서 속성을 바꾸는 매핑을 수행하면 TLB conflict가 발생하는 버그가 발견되었다. 따라서 이 영역에 대해서 contiguous 매핑을 하지 않도록 수정하였다.

- 코드 라인 29~30에서 커널 이미지의 초기화 코드 영역을 커널 실행 페이지 타입으로 매핑한다.

- 코드 라인 31~32에서 커널 이미지의 초기화 데이터 영역을 커널 페이지 타입으로 매핑한다.

- 코드 라인 33에서 커널 이미지의 일반 데이터 영역을 커널 페이지 타입으로 매핑한다.

- 커널 영역간에는 가드 페이지를 추가하지 않지만, 커널의 마지막 리니어 매핑 영역은 일반 vmalloc 할당 공간과 분리하기 위해 가드 페이지를 추가한다.

- 코드 라인 35~42에서 커널 이미지와 fixmap 공간이 같은 pgd 엔트리를 사용하지 않는 일반적인 경우이다. 이러한 경우 init_pg_dir에 구성되었던 fixmap 테이블을 swapper_pg_dir로 옮긴다.

- early_fixmap_init() 함수를 통해 init_pg_dir을 통해 이미 구성하였던 fixmap용 bm_pud, bm_pmd 및 bm_pud 간의 연결 중 init_pg_dir을 제외하고 swapper_pg_dir 쪽으로 연결을 옮긴다.

- 코드 라인 43~58에서 커널 이미지와 fixmap 공간이 같은 pgd 엔트리를 사용하는 특별한 경우이다. 이 경우는 4 단계의 16K 페이지 테이블 구성을 사용하는 경우에만 발생한다. 이 경우 fixmap이 구성된 bm_pmd 테이블을 swapper_pg_dir의 새 pgd(pud) 엔트리에 연결한다. 그런 후 pud 테이블의 매핑을 해제한다.

- 코드 라인 63에서 페이지 테이블을 복제하여 KASAN용 shodow 페이지 테이블을 만든다.

다음과 같이 커널 이미지를 덤프하여 head.text 섹션에 위치한 head.S 어셈블리 커널 코드가 시작됨을 알 수 있다. 또한 .text 섹션은 커널 코드가 담기는 영역이며 .rodata 섹션에는 읽기 전용 데이터가 담긴다.

- KASLR 커널 옵션을 사용하지 않는 디폴트 상태의 커널 이미지(.head.text)가 위치할 가상 주소의 위치는 0xffff_0000_1008_0000 임을 확인할 수 있다. 0x1000_0000을 띄운 이유는 이사이에 모듈과 bpf_jit 영역으로 각각 128M씩 사용한다. 또한 x08_0000은 로드된 커널 이미지의 시작 offset이다.

$ aarch64-linux-gnu-objdump -x vmlinux

vmlinux: file format elf64-littleaarch64

vmlinux

architecture: aarch64, flags 0x00000112:

EXEC_P, HAS_SYMS, D_PAGED

start address 0xffff000010080000

Program Header:

LOAD off 0x0000000000010000 vaddr 0xffff000010080000 paddr 0xffff000010080000 align 2**16

filesz 0x0000000000a7c7c0 memsz 0x0000000000a7c7c0 flags r-x

LOAD off 0x0000000000a90000 vaddr 0xffff000010b00000 paddr 0xffff000010b00000 align 2**16

filesz 0x0000000000831a00 memsz 0x00000000008d91a8 flags rwx

NOTE off 0x0000000000fc8598 vaddr 0xffff000011038598 paddr 0xffff000011038598 align 2**2

filesz 0x000000000000003c memsz 0x000000000000003c flags r--

STACK off 0x0000000000000000 vaddr 0x0000000000000000 paddr 0x0000000000000000 align 2**4

filesz 0x0000000000000000 memsz 0x0000000000000000 flags rw-

private flags = 0:

Sections:

Idx Name Size VMA LMA File off Algn

0 .head.text 00001000 ffff000010080000 ffff000010080000 00010000 2**12

CONTENTS, ALLOC, LOAD, READONLY, CODE

1 .text 00a7b7c0 ffff000010081000 ffff000010081000 00011000 2**11

CONTENTS, ALLOC, LOAD, READONLY, CODE

2 .rodata 004e78a0 ffff000010b00000 ffff000010b00000 00a90000 2**12

CONTENTS, ALLOC, LOAD, DATA

3 .pci_fixup 00002170 ffff000010fe78a0 ffff000010fe78a0 00f778a0 2**4

CONTENTS, ALLOC, LOAD, READONLY, DATA

4 __ksymtab 00009920 ffff000010fe9a10 ffff000010fe9a10 00f79a10 2**3

CONTENTS, ALLOC, LOAD, READONLY, DATA

5 __ksymtab_gpl 0000b2c0 ffff000010ff3330 ffff000010ff3330 00f83330 2**3

CONTENTS, ALLOC, LOAD, READONLY, DATA

6 __ksymtab_strings 00033801 ffff000010ffe5f0 ffff000010ffe5f0 00f8e5f0 2**0

CONTENTS, ALLOC, LOAD, READONLY, DATA

7 __param 00003660 ffff000011031df8 ffff000011031df8 00fc1df8 2**3

CONTENTS, ALLOC, LOAD, READONLY, DATA

8 __modver 00000ba8 ffff000011035458 ffff000011035458 00fc5458 2**3

CONTENTS, ALLOC, LOAD, READONLY, DATA

9 __ex_table 00002598 ffff000011036000 ffff000011036000 00fc6000 2**3

CONTENTS, ALLOC, LOAD, READONLY, DATA

10 .notes 0000003c ffff000011038598 ffff000011038598 00fc8598 2**2

CONTENTS, ALLOC, LOAD, READONLY, DATA

11 .init.text 000649a4 ffff000011040000 ffff000011040000 00fd0000 2**3

CONTENTS, ALLOC, LOAD, READONLY, CODE

(...생략...)

29 .debug_loc 00c6b58f 0000000000000000 0000000000000000 0d5146a0 2**0

map_kernel_segment()

arch/arm64/mm/mmu.c

static void __init map_kernel_segment(pgd_t *pgdp, void *va_start, void *va_end,

pgprot_t prot, struct vm_struct *vma,

int flags, unsigned long vm_flags)

{

phys_addr_t pa_start = __pa_symbol(va_start);

unsigned long size = va_end - va_start;

BUG_ON(!PAGE_ALIGNED(pa_start));

BUG_ON(!PAGE_ALIGNED(size));

__create_pgd_mapping(pgdp, pa_start, (unsigned long)va_start, size, prot,

early_pgtable_alloc, flags);

if (!(vm_flags & VM_NO_GUARD))

size += PAGE_SIZE;

vma->addr = va_start;

vma->phys_addr = pa_start;

vma->size = size;

vma->flags = VM_MAP | vm_flags;

vma->caller = __builtin_return_address(0);

vm_area_add_early(vma);

}

요청 가상 주소 범위를 가상 주소에 해당하는 물리 주소에 prot 메모리 타입으로 매핑하고, 이 영역은 vm_struct 구조체에 담아 전역 vmlist에 담아둔다.

- 코드 라인 11~12에서 요청 가상 주소 범위 @va_start ~ @va_end에 해당하는 물리 주소에 prot 메모리 타입으로 매핑한다.

- 코드 라인 14~23에서 구성된 vm_struct 구조체를 전역 vmlist에 담아둔다. 담아둔 리스트는 나중에 슬랩 메모리 할당자가 활성화된 이후에 vmalloc_init( ) 함수가 호출되면서 이를 활용한다.

메모리 매핑

map_mem()

arch/arm64/mm/mmu.c

static void __init map_mem(pgd_t *pgdp)

{

phys_addr_t kernel_start = __pa_symbol(_text);

phys_addr_t kernel_end = __pa_symbol(__init_begin);

struct memblock_region *reg;

int flags = 0;

u64 i;

if (rodata_full || debug_pagealloc_enabled())

flags = NO_BLOCK_MAPPINGS | NO_CONT_MAPPINGS;

/*

* Take care not to create a writable alias for the

* read-only text and rodata sections of the kernel image.

* So temporarily mark them as NOMAP to skip mappings in

* the following for-loop

*/

memblock_mark_nomap(kernel_start, kernel_end - kernel_start);

#ifdef CONFIG_KEXEC_CORE

if (crashk_res.end)

memblock_mark_nomap(crashk_res.start,

resource_size(&crashk_res));

#endif

/* map all the memory banks */

for_each_mem_range(i, &start, &end) {

if (start >= end)

break;

/*

* The linear map must allow allocation tags reading/writing

* if MTE is present. Otherwise, it has the same attributes as

* PAGE_KERNEL.

*/

__map_memblock(pgdp, start, end, PAGE_KERNEL, flags);

}

/*

* Map the linear alias of the [_text, __init_begin) interval

* as non-executable now, and remove the write permission in

* mark_linear_text_alias_ro() below (which will be called after

* alternative patching has completed). This makes the contents

* of the region accessible to subsystems such as hibernate,

* but protects it from inadvertent modification or execution.

* Note that contiguous mappings cannot be remapped in this way,

* so we should avoid them here.

*/

__map_memblock(pgdp, kernel_start, kernel_end,

PAGE_KERNEL, NO_CONT_MAPPINGS);

memblock_clear_nomap(kernel_start, kernel_end - kernel_start);

#ifdef CONFIG_KEXEC_CORE

/*

* Use page-level mappings here so that we can shrink the region

* in page granularity and put back unused memory to buddy system

* through /sys/kernel/kexec_crash_size interface.

*/

if (crashk_res.end) {

__map_memblock(pgdp, crashk_res.start, crashk_res.end + 1,

PAGE_KERNEL,

NO_BLOCK_MAPPINGS | NO_CONT_MAPPINGS);

memblock_clear_nomap(crashk_res.start,

resource_size(&crashk_res));

}

#endif

}

memory memblock에 등록된 각 메모리 영역을 pgd에 매핑한다.

- 코드 라인 9~10에서 “rodata=full” 커멘드 라인 파라메터가 주어지거나 CONFIG_DEBUG_PAGEALLOC 커널 옵션과 “debug_pagealloc=”이 설정된 경우 커널 영역은 writable 페이지가 된다. 이러한 경우 블럭(huge: pmd 타입 2M 섹션, pud 타입 1G 섹션) 매핑과 리니어 매핑을 하지 못하도록 플래그를 설정한다.

- CONFIG_DEBUG_PAGEALLOC 및 “debug_pagealloc=”

- KASAN(Kernel Address Sanitizer)보다는 빠른 페이지 메모리 할당에 대한 디버그를 사용하게 한다.

- 참고: Debugging | kernel.org

- NO_BLOCK_MAPPINGS

- 블럭(huge) 매핑을 하지 못하게 제한하는 플래그

- pmd 타입은 2M 섹션

- pud 타입은 1G 섹션

- NO_CONT_MAPPINGS

- 연속된 물리 페이지의 매핑 시 TLB 엔트리의 contiguous 비트를 설정하여 TLB 엔트리를 절약할 수 있는데 이를 못하게 제한하는 플래그

- 코드 라인 18에서 임시로 커널 memblock 영역을 nomap 플래그를 설정하여 아래 루프에서 매핑하지 못하도록 한다.

- 예) 4G의 물리 메모리가 1건이 memory 타입의 memblock에 등록되어 있는 경우 잠시 3 건의 영역으로 isolation 된다.

- 수행 전

- regions[0].base=0x4000_0000. size=0x1_0000_0000, flag=0

- 수행 후

- regions[0].base=0x4000_0000. size=0x8_0000, flag=0

- regions[0].base=0x4008_0000. size: 0xfc_0000, flag=4(no-map)

- regions[0].base=0x4104_0000. size: 0xfefc_0000, flag=0

- 코드 라인 20~22에서 crash kernel 영역도 nomap 플래그를 설정한다.

- 코드 라인 26~35에서 memory memblock에 등록된 각 영역에 대해 루프를 돌며 해당 영역을 태그(MTE)가 포함된 커널 페이지 속성(PAGE_KERNEL_TAGGED)으로 페이지 테이블에 매핑한다.

- 코드 라인 47~48에서 커널 영역을 커널 페이지 속성으로 리니어 영역에 매핑하되 contiguous 매핑을 허용하지 않는다.

- 리니어 매핑 영역에 커널 이미지를 매핑하여 놔두는 이유

- 코드 라인 49에서 임시로 커널 memblock 영역에 nomap 플래그를 설정한 것을 제거한다.

- 코드 라인 57~63에서 crash kernel 영역을 커널 페이지로 매핑하되 블럭 매핑과 리니어 매핑을 하지 않는다. 그런 후 memblock에 임시로 설정한 nomap 플래그를 제거한다.

다음 그림은 물리 주소의 메모리들과 커널이미지가 커널 영역에 해당하는 각각의 가상 주소에 매핑되는 것을 알 수 있다.

- 녹색으로 표시된 메모리 영역의 블럭들은 리니어 매핑 영역에 매핑된다.

- 황색으로 표시된 커널 영역의 블럭은 리니어 매핑 영역과 kimage 영역에 이중 매핑된다.

_ _map_memblock()

arch/arm64/mm/mmu.c

static void __init __map_memblock(pgd_t *pgdp, phys_addr_t start,

phys_addr_t end, pgprot_t prot, int flags)

{

__create_pgd_mapping(pgdp, start, __phys_to_virt(start), end - start,

prot, early_pgtable_alloc, flags);

}

pgd 페이지 테이블을 가리키는 포인터 @pgdp에 물리 주소 범위 @start ~ @end를 @flags 값을 사용하여 @prot 속성으로 매핑한다. 커널 부트업 타임에 버디 시스템 등의 정규 페이지 할당자가 아직 활성화되지 않았을 때 early 메모리 할당자인 memblock을 사용하여 페이지 테이블을 할당한다.

early_pgtable_alloc()

arch/arm64/mm/mmu.c

static phys_addr_t __init early_pgtable_alloc(int shift)

{

phys_addr_t phys;

void *ptr;

phys = memblock_phys_alloc(PAGE_SIZE, PAGE_SIZE);

if (!phys)

panic("Failed to allocate page table page\n");

/*

* The FIX_{PGD,PUD,PMD} slots may be in active use, but the FIX_PTE

* slot will be free, so we can (ab)use the FIX_PTE slot to initialise

* any level of table.

*/

ptr = pte_set_fixmap(phys);

memset(ptr, 0, PAGE_SIZE);

/*

* Implicit barriers also ensure the zeroed page is visible to the page

* table walker

*/

pte_clear_fixmap();

return phys;

}

페이지 테이블 용도로 사용할 싱글 페이지를 할당하여 0으로 초기화한 후 페이지의 물리 주소를 리턴한다. 0으로 초기화할 때 커널이 사용할 메모리들은 아직 매핑되어 있지 않으므로 접근할 수가 없다. 따라서 임시로 가상 주소를 사용하여 0으로 초기화하기 위해 fixmap 영역의 FIX_PTE 주소에 임시로 매핑하는 방법을 사용한다

- 코드 라인 6~8에서 커널 페이지 테이블로 사용할 하나의 페이지를 memblock으로부터 할당받는다.

- 코드 라인 15~25에서 fixmap의 FIX_PTE 주소에 매핑한 후 해당 페이지를 0으로 클리어하고, 다시 매핑 해제한 후 물리 주소를 리턴한다.

페이지 테이블 매핑

pgd 테이블에 매핑

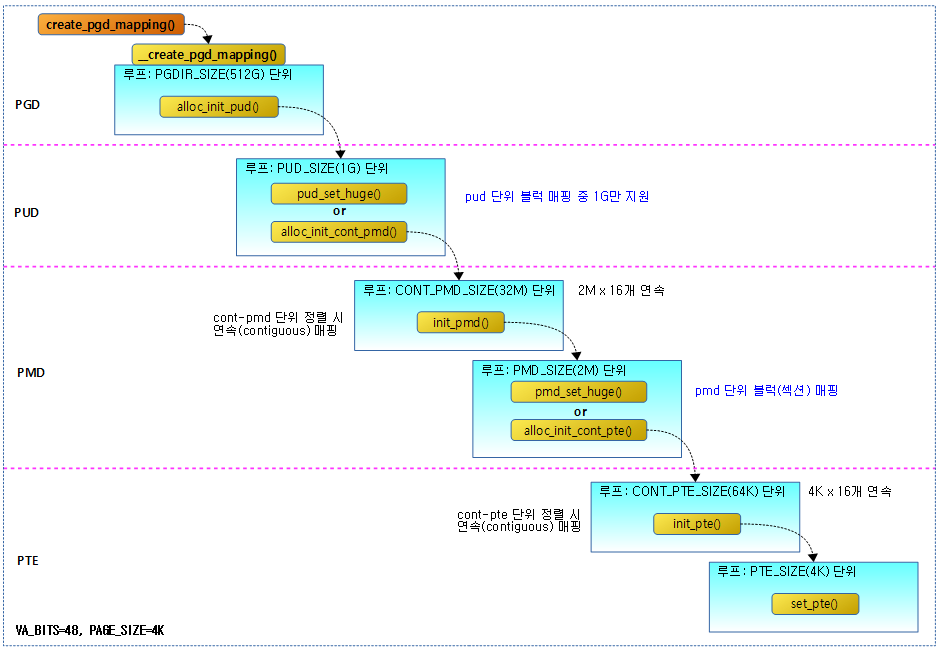

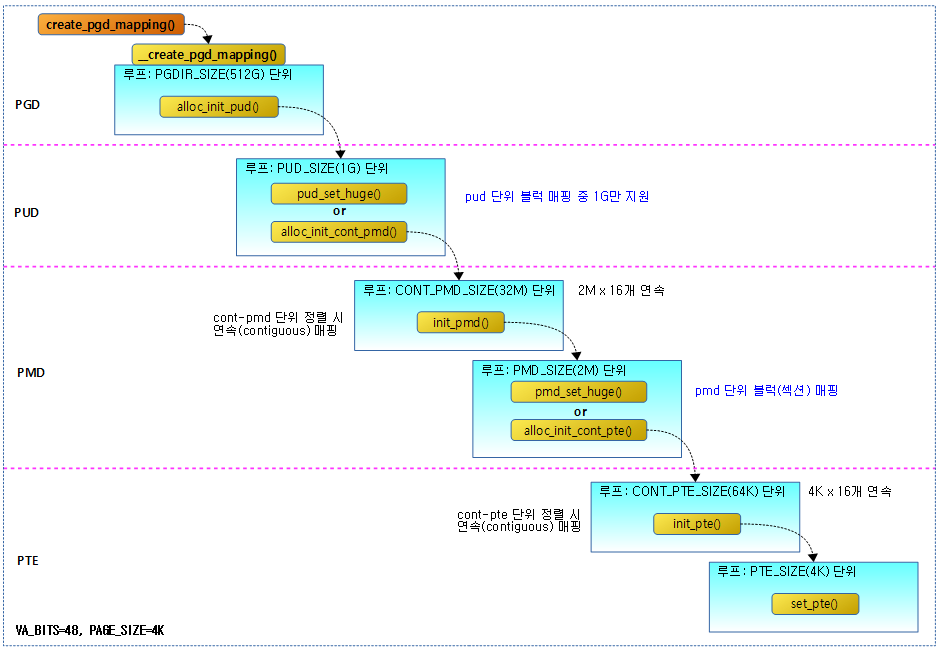

다음 그림은 물리 주소를 가상 주소로 요청하는 사이즈만큼 매핑하는 create_pgd_mapping() 함수의 호출 관계를 보여준다.

create_pgd_mapping()

arch/arm64/mm/mmu.c

void __init create_pgd_mapping(struct mm_struct *mm, phys_addr_t phys,

unsigned long virt, phys_addr_t size,

pgprot_t prot, bool page_mappings_only)

{

int flags = 0;

BUG_ON(mm == &init_mm);

if (page_mappings_only)

flags = NO_BLOCK_MAPPINGS | NO_CONT_MAPPINGS;

__create_pgd_mapping(mm->pgd, phys, virt, size, prot,

pgd_pgtable_alloc, flags);

}

유저 페이지 테이블의 가상 주소 @virt에서 @size에 해당하는 엔트리에 물리 주소 @phy를 @prot 속성으로 매핑한다. 인자로 주어진 @page_mappings_only가 true인 경우 개별 페이지 매핑만 지원한다. 즉 블럭(섹션) 매핑과 리니어 연속 매핑을 지원하지 않는다.

__create_pgd_mapping()

arch/arm64/mm/mmu.c

static void __create_pgd_mapping(pgd_t *pgdir, phys_addr_t phys,

unsigned long virt, phys_addr_t size,

pgprot_t prot,

phys_addr_t (*pgtable_alloc)(int),

int flags)

{

unsigned long addr, length, end, next;

pgd_t *pgdp = pgd_offset_raw(pgdir, virt);

/*

* If the virtual and physical address don't have the same offset

* within a page, we cannot map the region as the caller expects.

*/

if (WARN_ON((phys ^ virt) & ~PAGE_MASK))

return;

phys &= PAGE_MASK;

addr = virt & PAGE_MASK;

length = PAGE_ALIGN(size + (virt & ~PAGE_MASK));

end = addr + length;

do {

next = pgd_addr_end(addr, end);

alloc_init_pud(pgdp, addr, next, phys, prot, pgtable_alloc,

flags);

phys += next - addr;

} while (pgdp++, addr = next, addr != end);

}

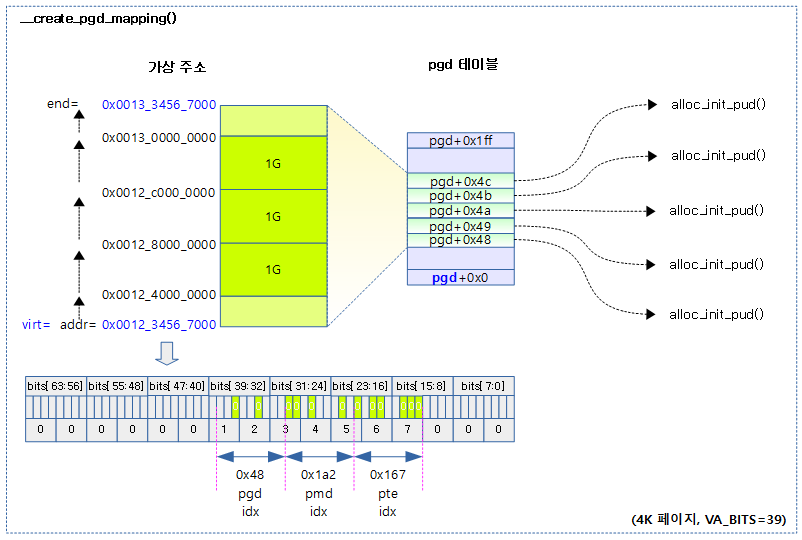

페이지 테이블 @pgdir에서 가상 주소 @virt 부터 @size 만큼에 해당하는 pgd 테이블 엔트리에 물리 주소 @phys 부터 매핑한다. 요청 범위에 대해 pgd 사이즈 단위로 순회하며 각각의 단위 매핑을 처리하기 위해 다음 레벨인 pud 테이블 매핑을 수행하러 alloc_init_pud() 함수를 호출한다. 연결될 하위 페이지 테이블을 할당받아야 할 때 인자로 전달받은 pgtable_alloc( ) 함수를 호출하여 페이지 테이블을 할당한다.

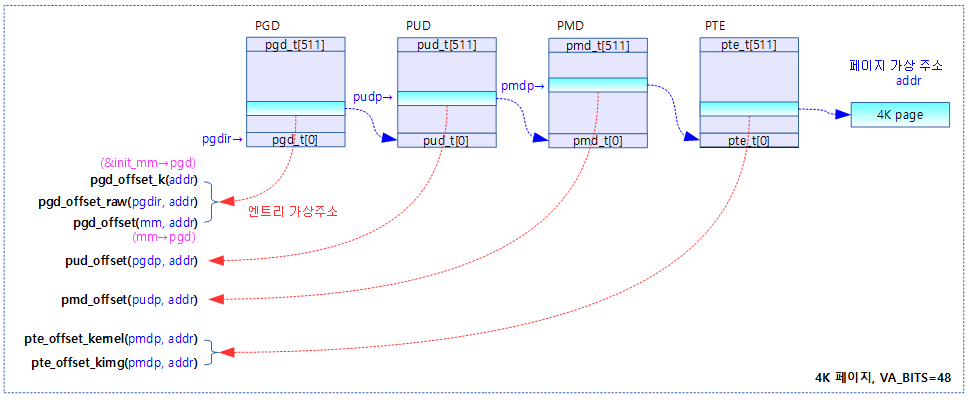

- 코드 라인 8에서 pgd 페이지 테이블 @pgdir 에서 가상 주소 @virt에 해당하는 pgd 엔트리 포인터를 알아온다.

- 코드 라인 17~21에서 물리 주소를 페이지 단위로 내림 정렬하고, 가상 주소를 페이지 단위로 내림 정렬하여 addr에 설정한다. 그리고 length에 매핑할 페이지 바이트 수를 계산하여 담고, end에 매핑의 끝 가상 주소를 담는다.

- 코드 라인 22~23에서 다음 처리할 pgd 엔트리를 구해둔다

- 매핑 진행 중인 가상 주소(addr)와 가상 끝 주소(end) 범위 내에서 다음 pgd 엔트리에 해당하는 가상 주소를 구한다. 만일 더 이상 처리할 수 없으면 가상 끝 주소(end)를 리턴한다.

- 코드 라인 24~25에서 가상 주소(addr)에 해당하는 pgd 엔트리가 없으면 pud 테이블을 생성하고 이를 가리키게 한다.

- 코드 라인 26에서 루프를 순회하기 위해 다음에 매핑할 pgd 엔트리의 물리 주소를 구한다.

- 코드 라인 27에서 다음 pgd 엔트리를 가리키도록 포인터를 증가시키고, 처리할 가상 주소(addr)에 next를 설정한다. 그런 후 매핑이 아직 다 완료되지 않았으면 루프를 돈다.

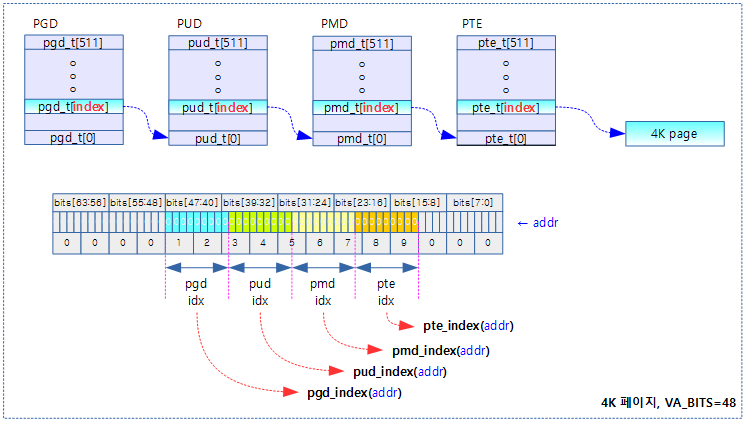

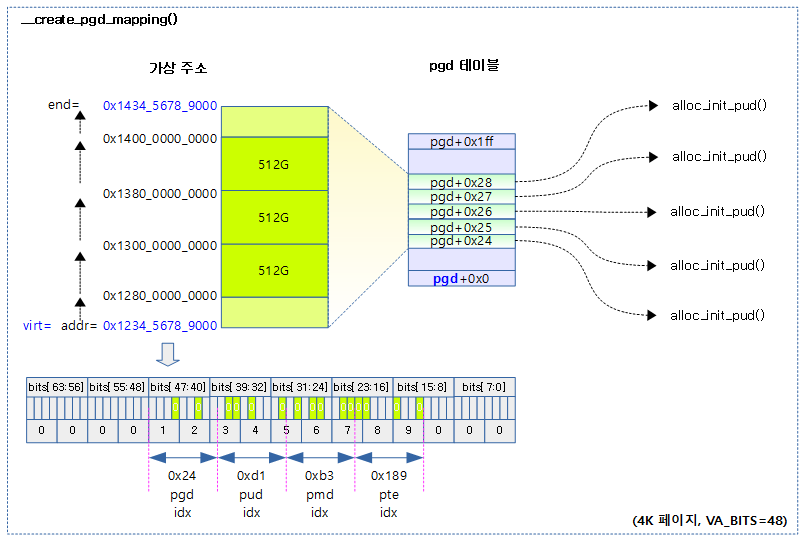

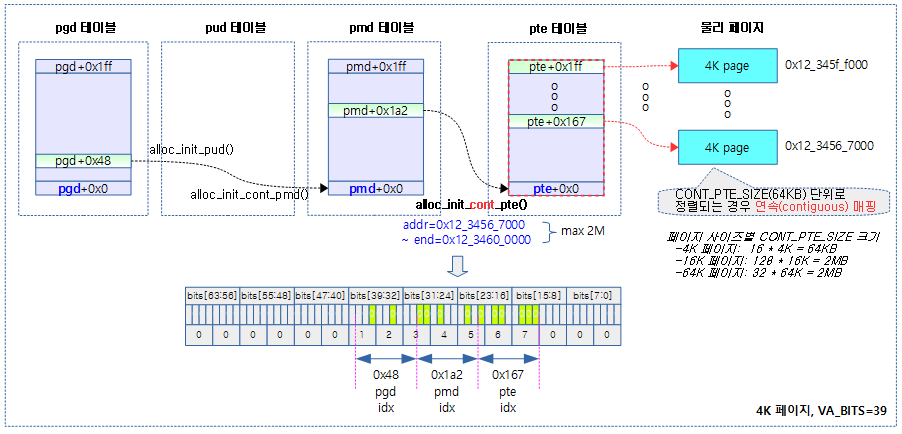

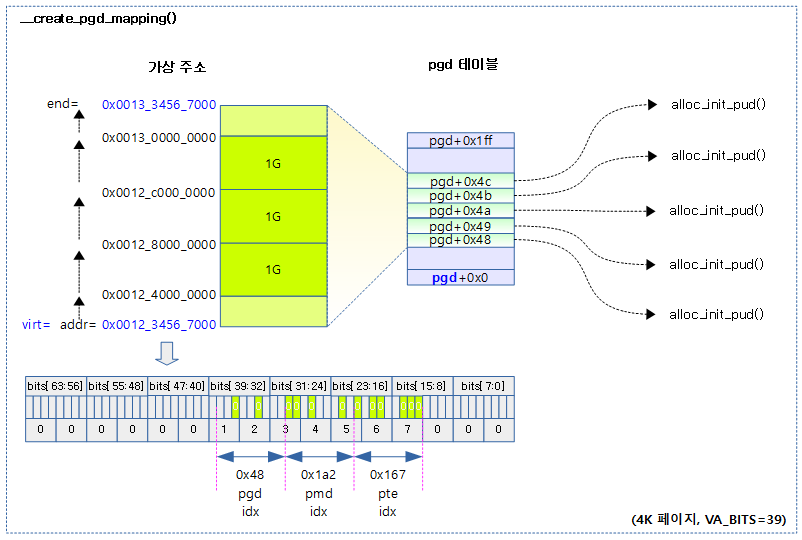

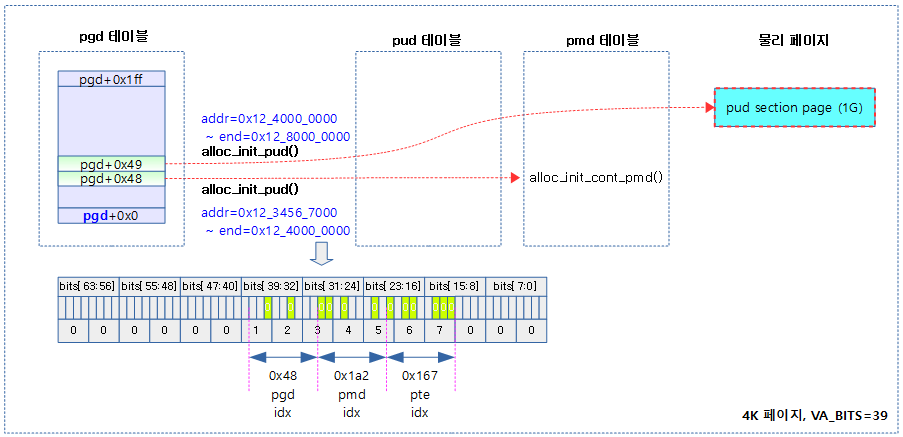

다음 그림은 4K 페이지, VA_BITS = 39를 사용한 구성으로 3 레벨의 페이지 테이블을 사용한다. __create_pgd_mapping() 함수를 통해 virt 주소부터 size만큼 pgd 엔트리를 구성하고 각 pgd 엔트리마다 alloc_init_pud( ) 함수를 호출하는 모습을 보여준다.

- pgd 엔트리는 pud 엔트리와 동일하며 하나당 1G 가상 공간을 관리한다.

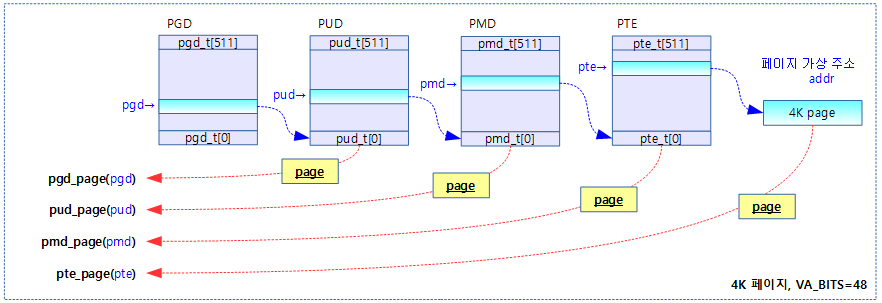

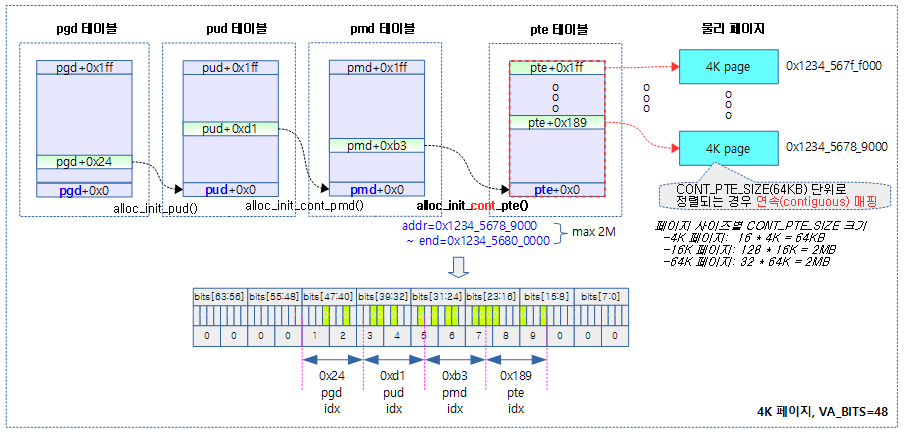

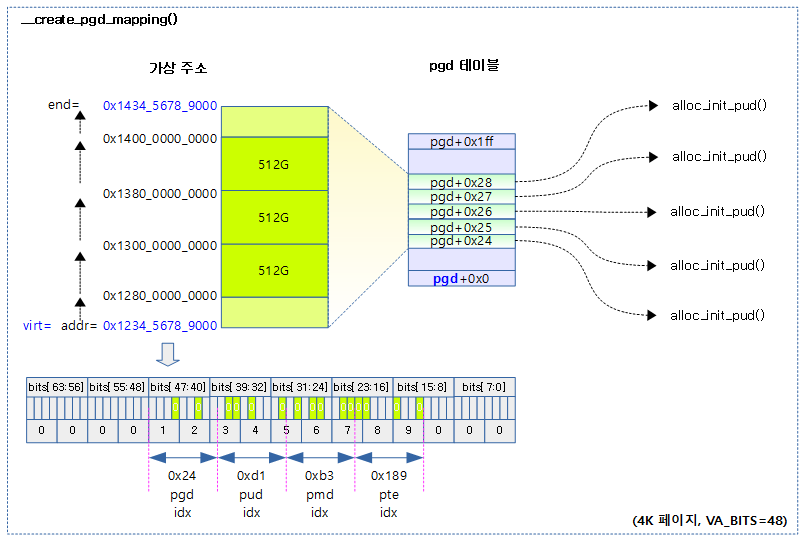

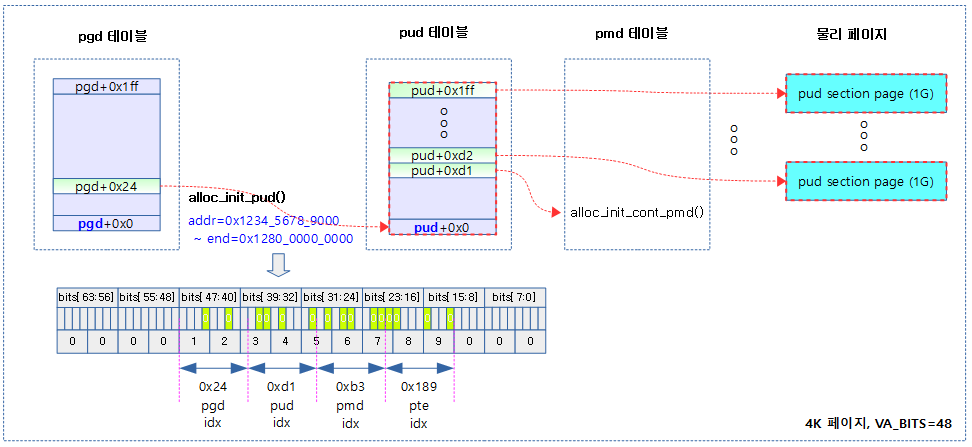

다음 그림은 4K 페이지, VA_BITS = 48을 사용한 구성으로 4레벨의 페이지 테이블을 사용한다. __create_pgd_mapping() 함수를 통해 virt 주소부터 size만큼 pgd 엔트리를 구성하고 각 pgd 엔트리마다 alloc_init_pud( ) 함수를 호출하는 모습을 보여준다.

- pgd 엔트리 하나당 512G 가상 공간을 관리한다.

pud 테이블 할당 및 초기화

alloc_init_pud()

arch/arm64/mm/mmu.c

static void alloc_init_pud(pgd_t *pgdp, unsigned long addr, unsigned long end,

phys_addr_t phys, pgprot_t prot,

phys_addr_t (*pgtable_alloc)(int),

int flags)

{

unsigned long next;

pud_t *pudp;

p4d_t *p4dp = p4d_offset(pgdp, addr);

p4d_t p4d = READ_ONCE(*p4dp);

if (p4d_none(p4d)) {

phys_addr_t pud_phys;

BUG_ON(!pgtable_alloc);

pud_phys = pgtable_alloc(PUD_SHIFT);

__p4d_populate(p4dp, pud_phys, PUD_TYPE_TABLE);

p4d = READ_ONCE(*p4dp);

}

BUG_ON(p4d_bad(p4d));

pudp = pud_set_fixmap_offset(p4dp, addr);

do {

pud_t old_pud = READ_ONCE(*pudp);

next = pud_addr_end(addr, end);

/*

* For 4K granule only, attempt to put down a 1GB block

*/

if (use_1G_block(addr, next, phys) &&

(flags & NO_BLOCK_MAPPINGS) == 0) {

pud_set_huge(pudp, phys, prot);

/*

* After the PUD entry has been populated once, we

* only allow updates to the permission attributes.

*/

BUG_ON(!pgattr_change_is_safe(pud_val(old_pud),

READ_ONCE(pud_val(*pudp))));

} else {

alloc_init_cont_pmd(pudp, addr, next, phys, prot,

pgtable_alloc, flags);

BUG_ON(pud_val(old_pud) != 0 &&

pud_val(old_pud) != READ_ONCE(pud_val(*pudp)));

}

phys += next - addr;

} while (pudp++, addr = next, addr != end);

pud_clear_fixmap();

}

가상 주소 @addr ~ @end 범위에 물리 주소 @phys부터 @prot 속성으로 매핑한다. 요청 범위에 대해 pud 사이즈 단위로 순회하며 각각의 단위 매핑 공간이 1G 블럭 단위로 정렬되는 경우 블럭 매핑을 수행하고, 그렇지 않은 경우 pud 사이즈에 해당하는 공간을 처리하기 위해 다음 레벨인 pmd 테이블 매핑을 수행하러 alloc_init_cont_pmd()를 호출한다.

- 코드 라인 8~17에서 p4d 엔트리가 매핑되어 있지 않아 NULL인 경우에는 pud 테이블을 할당받아 연결한다.

- arm64의 경우 pgd 테이블과 p4d 테이블은 동일하다.

- 코드 라인 20에서 fixmap에 pud 테이블을 매핑한다.

- fixmap에서 pgd, pud, pmd, pte 테이블용으로 각각의 페이지가 준비되어 있는데, 할당받은 페이지 테이블이 memblock으로부터 막 할당받아 아직 가상 주소에 매핑되어 사용하지 않는 경우 임시로 가상 주소에 매핑시켜 사용할 수 있도록 준비된 페이지로 페이지 테이블의 첫 구성 시에 사용한다.

- 코드 라인 21~24에서 처리할 pud 엔트리에 대한 범위를 알아온다. 그 다음 주소는 next에 반환한다.

- 매핑 진행 중인 가상 주소(addr)와 가상 끝 주소(end) 범위 내에서 다음 pud 엔트리에 해당하는 가상 주소를 구한다. 만일 더 이상 처리할 수 없으면 가상 끝 주소(end)를 리턴한다.

- 코드 라인 29~38에서 4K 페이지 테이블을 사용하면서 1G 사이즈이면서 가상 주소, 물리 주소가 모두 1G 단위로 정렬된 경우 pud 타입 섹션 매핑을 한다.

- 코드 라인 39~45에서 가상 주소(addr)에 해당하는 pud 엔트리가 없으면 pmd 테이블을 생성하고 이를 가리키게 한다.

- 코드 라인 46~47에서 다음 가상 주소 addr에 해당하는 pud 엔트리를 처리하기 위해 루프를 돈다.

- 코드 라인 49에서 pud용 fixmap 페이지를 매핑 해제한다.

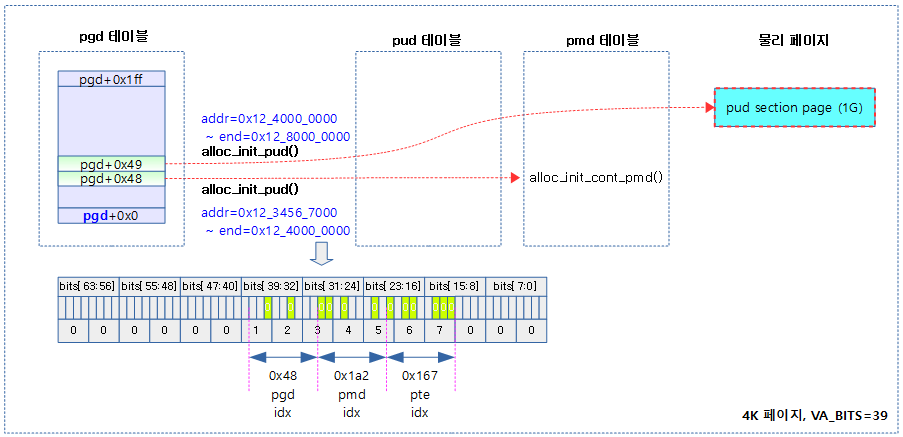

다음 그림은 4K 페이지, VA_BITS =39 커널 옵션을 사용한 경우 alloc_init_pud( ) 함수를 통해 addr~end 가상 주소 범위에 해당하는 pud 섹션 페이지가 매핑되거나 alloc_init_cont_pmd() 함수를 호출하는 과정을 보여준다(최종 pmd 및 pte 테이블 구성은 생략)

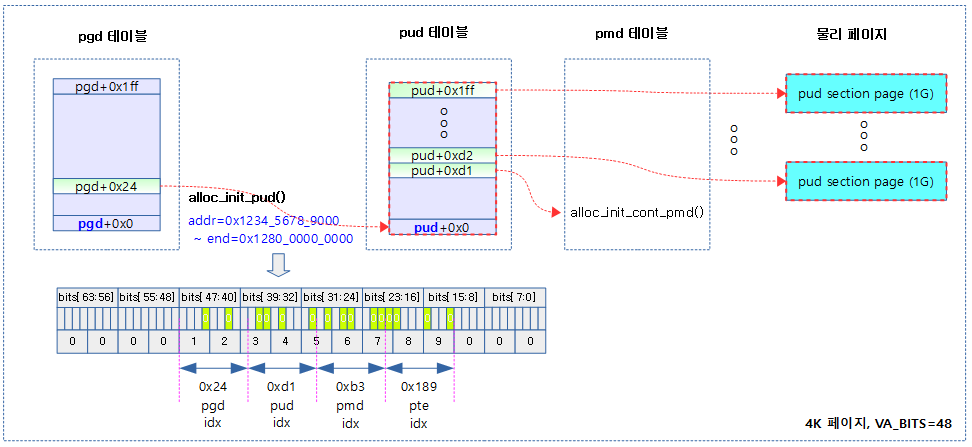

다음 그림은 4K 페이지, VA_BITS =48 커널 옵션을 사용한 경우 alloc_init_pud( ) 함수를 통해 addr~end 가상 주소 범위에 해당하는 pud 섹션 페이지가 매핑되거나 alloc_init_cont_pmd() 함수를 호출하는 과정을 보여준다(최종 pmd 및 pte 테이블 구성은 생략)

pmd 테이블 할당 및 초기화 -1-

pmd 및 pte 테이블은 pgd 및 pud 테이블과 다르게 contiguous 매핑이 가능하다. 이 함수에서는 pmd contiguous 매핑 사이즈 단위(pmd contiguous 최대 횟수 * pmd 사이즈)로 루프를 돌며 init_pmd() 함수를 호출한다.

alloc_init_cont_pmd()

arch/arm64/mm/mmu.c

static void alloc_init_cont_pmd(pud_t *pudp, unsigned long addr,

unsigned long end, phys_addr_t phys,

pgprot_t prot,

phys_addr_t (*pgtable_alloc)(int), int flags)

{

unsigned long next;

pud_t pud = READ_ONCE(*pudp);

/*

* Check for initial section mappings in the pgd/pud.

*/

BUG_ON(pud_sect(pud));

if (pud_none(pud)) {

phys_addr_t pmd_phys;

BUG_ON(!pgtable_alloc);

pmd_phys = pgtable_alloc(PMD_SHIFT);

__pud_populate(pudp, pmd_phys, PUD_TYPE_TABLE);

pud = READ_ONCE(*pudp);

}

BUG_ON(pud_bad(pud));

do {

pgprot_t __prot = prot;

next = pmd_cont_addr_end(addr, end);

/* use a contiguous mapping if the range is suitably aligned */

if ((((addr | next | phys) & ~CONT_PMD_MASK) == 0) &&

(flags & NO_CONT_MAPPINGS) == 0)

__prot = __pgprot(pgprot_val(prot) | PTE_CONT);

init_pmd(pudp, addr, next, phys, __prot, pgtable_alloc, flags);

phys += next - addr;

} while (addr = next, addr != end);

}

가상 주소 @addr ~ @end 범위에 물리 주소 @phys부터 @prot 속성으로 매핑한다. 요청 범위에 대해 cont pmd 사이즈 단위로 순회하며 cont pmd 사이즈에 해당하는 매핑을 수행하기 위해 init_pmd()를 호출한다. 만일 각각의 단위 매핑 공간이 cont pmd 단위로 사이즈와 가상 주소 및 물리 주소가 정렬되는 경우 속성에 연속(contiguous) 비트를 추가한다. 이렇게 연속 매핑 비트를 사용하는 경우 pmd 엔트리에 해당하는 TLB 엔트리를 절약할 수 있다.

- 코드 라인 13~19에서 pud 엔트리가 매핑되어 있지 않아 NULL이거나 pud 섹션 페이지 매핑(64K 페이지가 아니면서 3레벨 이상의 변환 테이블에서만 유효)된 경우 pmd 테이블을 할당받아 연결한다.

- 코드 라인 22~25에서 처리할 cont pmd 엔트리에 대한 범위를 알아온다. 그 다음 주소는 next에 반환한다.

- 루프를 돌며 매핑 진행 중인 가상 주소(addr)와 가상 끝 주소(end) 범위 내에서 다음 cont pmd 엔트리에 해당하는 가상 주소를 구한다. 만일 더 이상 처리할 수 없으면 가상 끝 주소(end)를 리턴한다.

- 예) 4K 페이지, VA_BITS=48 시스템에서 cont pmd 사이즈는 CONT_PMDS(16번) x PMD_SIZE(2M) = CONT_PMD_SIZE(32M)이다.

- 코드 라인 28~30에서 cont pmd 사이즈 이면서 가상 주소, 물리 주소가 모두 cont pmd 사이즈로 정렬된 경우 연속 매핑 플래그를 설정한다.

- 코드 라인 32에서 pmd 엔트리 아래에 연결된 pte 테이블을 생성하고 이를 가리키게 한다.

- 코드 라인 34~35에서 다음 가상 주소 addr에 해당하는 pmd 엔트리를 처리하기 위해 루프를 돈다.

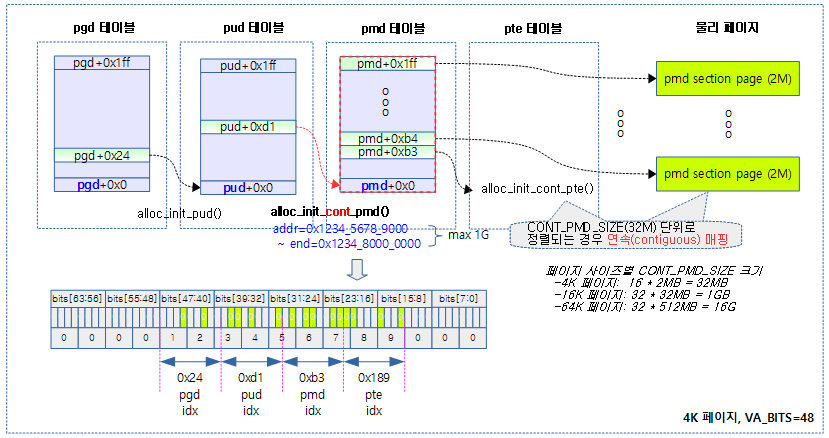

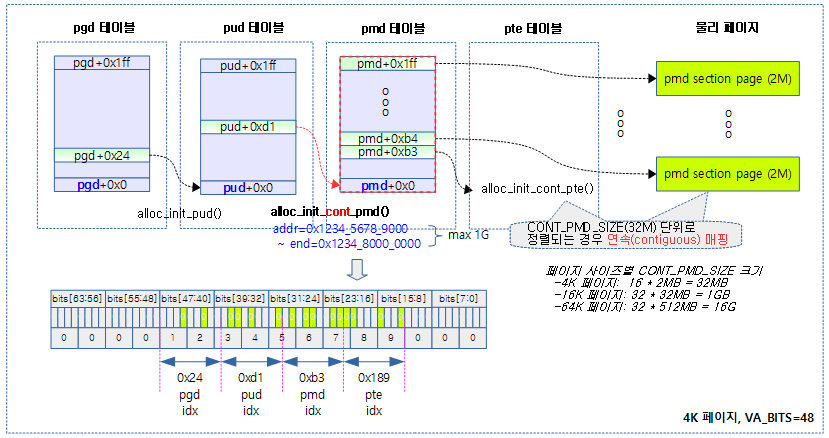

다음 그림은 4K 페이지, VA_BITS =39 커널 옵션을 사용한 경우 alloc_init_cont_pmd( ) 함수를 통해 addr~end 가상 주소에 해당하는 pmd 엔트리들에 pmd 섹션 페이지가 매핑되거나 alloc_init_pte() 함수를 호출하는 과정을 보여준다(최종 pte 테이블 구성은 생략).

다음 그림은 4K 페이지, VA_BITS =48 커널 옵션을 사용한 경우 alloc_init_cont_pmd() 함수를 통해 addr~end 가상 주소에 해당하는 pmd 엔트리들에 pmd 섹션 페이지가 매핑되거나 alloc_init_pte() 함수를 호출하는 과정을 보여준다(최종 pte 테이블 구성은 생략).

pmd 테이블 할당 및 초기화 -2-

init_pmd()

arch/arm64/mm/mmu.c

static void init_pmd(pud_t *pudp, unsigned long addr, unsigned long end,

phys_addr_t phys, pgprot_t prot,

phys_addr_t (*pgtable_alloc)(int), int flags)

{

unsigned long next;

pmd_t *pmdp;

pmdp = pmd_set_fixmap_offset(pudp, addr);

do {

pmd_t old_pmd = READ_ONCE(*pmdp);

next = pmd_addr_end(addr, end);

/* try section mapping first */

if (((addr | next | phys) & ~SECTION_MASK) == 0 &&

(flags & NO_BLOCK_MAPPINGS) == 0) {

pmd_set_huge(pmdp, phys, prot);

/*

* After the PMD entry has been populated once, we

* only allow updates to the permission attributes.

*/

BUG_ON(!pgattr_change_is_safe(pmd_val(old_pmd),

READ_ONCE(pmd_val(*pmdp))));

} else {

alloc_init_cont_pte(pmdp, addr, next, phys, prot,

pgtable_alloc, flags);

BUG_ON(pmd_val(old_pmd) != 0 &&

pmd_val(old_pmd) != READ_ONCE(pmd_val(*pmdp)));

}

phys += next - addr;

} while (pmdp++, addr = next, addr != end);

pmd_clear_fixmap();

}

가상 주소 @addr ~ @end 범위에 물리 주소 @phys부터 @prot 속성으로 매핑한다. 요청 범위에 대해 pmd 사이즈 단위로 순회하며 각각의 단위 매핑 공간이 섹션 단위로 정렬되는 경우 섹션 매핑을 수행하고, 그렇지 않은 경우 alloc_init_cont_pte() 함수를 호출하여 pte 레벨에서 매핑을 계속한다.

요청한 가상 주소 @addr ~ @end 범위의 pmd 엔트리에 대해 초기화를 수행한다. 필요시 pmd 섹션 블럭이나 pte 테이블을 생성하여 연결한다.

- 코드 라인 8에서 처리할 pmd 테이블을 fixmap에 매핑하고 가상주소 @addr에 해당하는 pmd 엔트리 포인터를 알아온다.

- 코드 라인 9~10에서 루프를 돌며 pmd 엔트리 값을 읽어 old_pmd에 저장해둔다.

- 코드 라인 12에서 다음 처리할 pmd 엔트리를 구해둔다.

- 가상 주소(addr)와 가상 끝 주소(end) 범위 내에서 다음 pmd 엔트리에 해당하는 가상 주소를 구한다. 만일 더 이상 처리할 수 없으면 가상 끝 주소(end)를 리턴한다.

- 코드 라인 15~24에서 pmd 사이즈 이면서 가상 주소, 물리 주소가 모두 pmd 사이즈로 정렬된 경우 pmd 타입 섹션 매핑을수행한다.

- 예) 4K 페이지, VA_BITS=48인 경우 pmd 사이즈는 2M이다.

- 코드 라인 25~31에서 다음 레벨 pte 테이블을 할당하고 범위 내의 페이지들을 매핑한다.

- 코드 라인 32~33에서 다음 처리할 pmd 엔트리를 위해 루프를 돈다.

- 코드 라인 35에서 pmd 테이블을 fixmap에서 해제한다.

pte 테이블 할당 및 초기화 -1-

pte 테이블도 contiguous 매핑이 가능하다.

alloc_init_cont_pte()

arch/arm64/mm/mmu.c

static void alloc_init_cont_pte(pmd_t *pmdp, unsigned long addr,

unsigned long end, phys_addr_t phys,

pgprot_t prot,

phys_addr_t (*pgtable_alloc)(int),

int flags)

{

unsigned long next;

pmd_t pmd = READ_ONCE(*pmdp);

BUG_ON(pmd_sect(pmd));

if (pmd_none(pmd)) {

phys_addr_t pte_phys;

BUG_ON(!pgtable_alloc);

pte_phys = pgtable_alloc(PAGE_SHIFT);

__pmd_populate(pmdp, pte_phys, PMD_TYPE_TABLE);

pmd = READ_ONCE(*pmdp);

}

BUG_ON(pmd_bad(pmd));

do {

pgprot_t __prot = prot;

next = pte_cont_addr_end(addr, end);

/* use a contiguous mapping if the range is suitably aligned */

if ((((addr | next | phys) & ~CONT_PTE_MASK) == 0) &&

(flags & NO_CONT_MAPPINGS) == 0)

__prot = __pgprot(pgprot_val(prot) | PTE_CONT);

init_pte(pmdp, addr, next, phys, __prot);

phys += next - addr;

} while (addr = next, addr != end);

}

가상 주소 @addr ~ @end 범위에 물리 주소 @phys부터 @prot 속성으로 매핑한다. 요청 범위에 대해 cont pte 사이즈 단위로 순회하며 cont pte 사이즈에 해당하는 매핑을 수행하기 위해 init_pte()를 호출한다. 만일 각각의 단위 매핑 공간이 cont pte 단위로 사이즈와 가상 주소 및 물리 주소가 정렬되는 경우 속성에 연속(contiguous) 비트를 추가한다. 이렇게 연속 매핑 비트를 사용하는 경우 pte 엔트리에 해당하는 TLB 엔트리를 절약할 수 있다.

- 코드 라인 8~17에서 pmd 엔트리가 매핑되어 있지 않아 NULL인 경우 pte 테이블을 할당받아 연결한다.

- 코드 라인 20~23에서 루프를 돌며 다음 처리할 pmd 엔트리를 구해둔다

- 매핑 진행 중인 가상 주소(addr)와 가상 끝 주소(end) 범위 내에서 다음 pmd 엔트리에 해당하는 가상 주소를 구한다. 만일 더 이상 처리할 수 없으면 가상 끝 주소(end)를 리턴한다.

- 코드 라인 26~28에서 cont pte사이즈 이면서 가상 주소, 물리 주소가 모두 cont pte 사이즈로 정렬된 경우 연속 매핑 플래그를 설정한다.

- 4K 페이지를 사용하는 경우 4K 페이지 * 16 = 64KB 단위

- 16K 페이지를 사용하는 경우 16K 페이지 * 128 = 2MB 단위

- 64K 페이지를 사용하는 경우 64K 페이지 * 32 = 2MB 단위

- 코드 라인 30에서 pte 엔트리와 해당 범위의 페이지들을 매핑한다.

- 코드 라인 32~33에서 다음 처리할 pmd 엔트리를 위해 루프를 돈다.

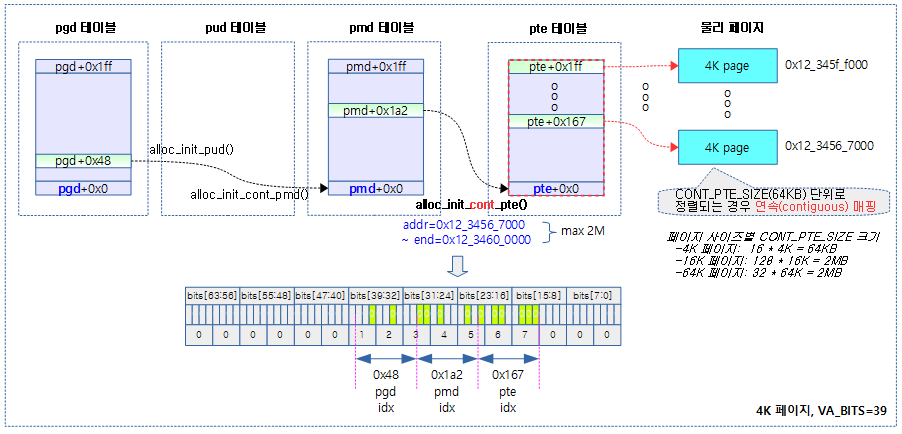

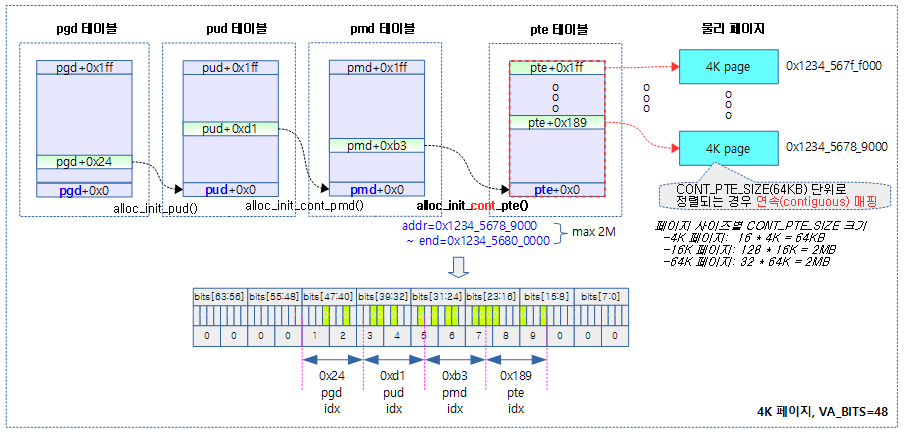

다음 그림은 4K 페이지, VA_BITS =39 커널 옵션을 사용한 경우 alloc_init_cont_pte( ) 함수를 통해 addr~end 가상 주소에 해당하는 pte 엔트리를 구성하고 최종 페이지와 매핑하는 것을 보여준다.

다음 그림은 4K 페이지, VA_BITS =48 커널 옵션을 사용한 경우 alloc_init_cont_pte( ) 함수를 통해 addr~end 가상 주소에 해당하는 pte 엔트리를 구성하고 최종 페이지와 매핑하는 것을 보여준다.

pte 테이블 할당 및 초기화 -2-

init_pte()

arch/arm64/mm/mmu.c

static void init_pte(pmd_t *pmdp, unsigned long addr, unsigned long end,

phys_addr_t phys, pgprot_t prot)

{

pte_t *ptep;

ptep = pte_set_fixmap_offset(pmdp, addr);

do {

pte_t old_pte = READ_ONCE(*ptep);

set_pte(ptep, pfn_pte(__phys_to_pfn(phys), prot));

/*

* After the PTE entry has been populated once, we

* only allow updates to the permission attributes.

*/

BUG_ON(!pgattr_change_is_safe(pte_val(old_pte),

READ_ONCE(pte_val(*ptep))));

phys += PAGE_SIZE;

} while (ptep++, addr += PAGE_SIZE, addr != end);

pte_clear_fixmap();

}

요청한 가상 주소 @addr ~ @end 범위의 pte 엔트리를 페이지와 매핑한다.

- 코드 라인 6에서 처리할 pte 테이블을 fixmap에 매핑하고 가상주소 @addr에 해당하는 pte 엔트리 포인터를 알아온다.

- 코드 라인 7~9에서 루프를 돌며 pte 엔트리 값을 읽어 old_pte에 저장해둔다.

- 코드 라인 11에서 pte 엔트리에 매핑할 페이지에 해당하는 물리 주소와 속성을 기록하여 매핑한다.

- 코드 라인 19~20에서 다음 처리할 pte 엔트리를 위해 루프를 돈다.

- 코드 라인 22에서 pte 테이블을 fixmap에서 해제한다.

테이블 연결(population)

pgd_populate()

include/asm-generic/pgtable-nop4d.h

#define pgd_populate(mm, pgd, p4d) do { } while (0)

p4d_populate()

arch/arm64/include/asm/pgalloc.h

static inline void p4d_populate(struct mm_struct *mm, p4d_t *p4dp, pud_t *pudp)

{

__p4d_populate(p4dp, __pa(pudp), PUD_TYPE_TABLE);

}

pgd 페이지 테이블 엔트리 포인터 @pgdp에 다음 레벨의 pud 테이블을 연결한다.

__p4d_populate()

arch/arm64/include/asm/pgalloc.h

static inline void __p4d_populate(pgd_t *p4dp, phys_addr_t pudp, pgdval_t prot)

{

set_p4d(p4dp, __p4d(__phys_to_p4d_val(pudp) | prot));

}

pgd 페이지 테이블 엔트리 포인터 @pgdp에 다음 레벨의 pud 테이블을 연결할 때 @prot 속성을 사용한다.

pud_populate()

arch/arm64/include/asm/pgalloc.h

static inline void pud_populate(struct mm_struct *mm, pud_t *pudp, pmd_t *pmdp)

{

__pud_populate(pudp, __pa(pmdp), PMD_TYPE_TABLE);

}

pud 페이지 테이블 엔트리 포인터 @pudp에 다음 레벨의 pmd 테이블을 연결한다.

__pud_populate()

arch/arm64/include/asm/pgalloc.h

static inline void __pud_populate(pud_t *pudp, phys_addr_t pmdp, pudval_t prot)

{

set_pud(pudp, __pud(__phys_to_pud_val(pmdp) | prot));

}

pud 페이지 테이블 엔트리 포인터 @pudp에 다음 레벨의 pmd 테이블을 연결할 때 @prot 속성을 사용한다.

pmd_populate()

arch/arm64/include/asm/pgalloc.h

static inline void

pmd_populate(struct mm_struct *mm, pmd_t *pmdp, pgtable_t ptep)

{

__pmd_populate(pmdp, page_to_phys(ptep), PMD_TYPE_TABLE);

}

pmd 페이지 테이블 엔트리 포인터 @pmdp에 다음 레벨의 pte 테이블을 연결한다.

__pmd_populate()

arch/arm64/include/asm/pgalloc.h

static inline void __pmd_populate(pmd_t *pmdp, phys_addr_t ptep,

pmdval_t prot)

{

set_pmd(pmdp, __pmd(__phys_to_pmd_val(ptep) | prot));

}

pmd 페이지 테이블 엔트리 포인터 @pmdp에 다음 레벨의 pte 테이블을 연결할 때 @prot 속성을 사용한다.

테이블 엔트리 매핑/해제

테이블 엔트리 매핑

set_pgd()

include/asm-generic/pgtable-nop4d.h

/*

* (p4ds are folded into pgds so this doesn't get actually called,

* but the define is needed for a generic inline function.)

*/

#define set_pgd(pgdptr, pgdval) set_p4d((p4d_t *)(pgdptr), (p4d_t) { pgdval })

arm64의 경우 pgd 테이블 역할을 p4d 테이블이 수행하도록 곧바로 set_p4d() 함수를 호출한다.

set_p4d()

arch/arm64/include/asm/pgtable.h

static inline void set_p4d(p4d_t *p4dp, p4d_t p4d)

{

if (in_swapper_pgdir(p4dp)) {

set_swapper_pgd((pgd_t *)p4dp, __pgd(p4d_val(pgd)));

return;

}

WRITE_ONCE(*p4dp, p4d);

dsb(ishst);

isb();

}

pgd 테이블 엔트리 포인터 @pgdp에 @pgd 값을 기록하여 매핑한다.

- 커널 영역은 내부 공유(inner share) 영역에 포함된 cpu들이 공유하여 사용 중인 영역이다. 그러므로 이 cpu들을 한꺼번에 TLB 및 인스트럭션 캐시 등에 대해 동기화하는 작업이 필요하다. 따라서 TLB 캐시 작업이 완료될 때까지 기다리도록 dsb 배리어를 수행한다. 그 후 isb 베리어를 사용하여 파이프라인을 비운다.

set_swapper_pgd()

arch/arm64/mm/mmu.c

void set_swapper_pgd(pgd_t *pgdp, pgd_t pgd)

{

pgd_t *fixmap_pgdp;

spin_lock(&swapper_pgdir_lock);

fixmap_pgdp = pgd_set_fixmap(__pa_symbol(pgdp));

WRITE_ONCE(*fixmap_pgdp, pgd);

/*

* We need dsb(ishst) here to ensure the page-table-walker sees

* our new entry before set_p?d() returns. The fixmap's

* flush_tlb_kernel_range() via clear_fixmap() does this for us.

*/

pgd_clear_fixmap();

spin_unlock(&swapper_pgdir_lock);

}

set_pud()

arch/arm64/include/asm/pgtable.h

static inline void set_pud(pud_t *pudp, pud_t pud)

{

#ifdef __PAGETABLE_PUD_FOLDED

if (in_swapper_pgdir(pudp)) {

set_swapper_pgd((pgd_t *)pudp, __pgd(pud_val(pud)));

return;

}

#endif /* __PAGETABLE_PUD_FOLDED */

WRITE_ONCE(*pudp, pud);

if (pud_valid(pud)) {

dsb(ishst);

isb();

}

}

pud 테이블 엔트리 포인터 @pudp에 @pud 값을 기록하여 매핑한다.

set_pmd()

arch/arm64/include/asm/pgtable.h

static inline void set_pmd(pmd_t *pmdp, pmd_t pmd)

{

#ifdef __PAGETABLE_PMD_FOLDED

if (in_swapper_pgdir(pmdp)) {

set_swapper_pgd((pgd_t *)pmdp, __pgd(pmd_val(pmd)));

return;

}

#endif /* __PAGETABLE_PMD_FOLDED */

WRITE_ONCE(*pmdp, pmd);

if (pmd_valid(pmd)) {

dsb(ishst);

isb();

}

}

pmd 테이블 엔트리 포인터 @pmdp에 @pmd 값을 기록하여 매핑한다.

set_pte()

arch/arm64/include/asm/pgtable.h

static inline void set_pte(pte_t *ptep, pte_t pte)

{

WRITE_ONCE(*ptep, pte);

/*

* Only if the new pte is valid and kernel, otherwise TLB maintenance

* or update_mmu_cache() have the necessary barriers.

*/

if (pte_valid_not_user(pte)) {

dsb(ishst);

isb();

}

}

pte 테이블 엔트리 포인터 @ptep에 @pte 값을 기록하여 매핑한다.

테이블 엔트리 매핑 해제

pgd_clear()

include/asm-generic/pgtable-nop4d.h

static inline void pgd_clear(pgd_t *pgd) { }

arm64의 경우 pgd 테이블 역할을 p4d 테이블이 수행하므로 pgd 테이블의 작업을 아무것도 하지 못하게 한다.

p4d_clear()

arch/arm64/include/asm/pgtable.h

static inline void p4d_clear(pgd_t *p4dp)

{

set_p4d(p4dp, __p4d(0));

}

@pgdp 엔트리 포인터에 0을 기록하여 매핑을 해제한다.

pud_clear()

arch/arm64/include/asm/pgtable.h

static inline void pud_clear(pud_t *pudp)

{

set_pud(pudp, __pud(0));

}

@pudp 엔트리 포인터에 0을 기록하여 매핑을 해제한다.

pmd_clear()

arch/arm64/include/asm/pgtable.h

static inline void pmd_clear(pmd_t *pmdp)

{

set_pmd(pmdp, __pmd(0));

}

@pmdp 엔트리 포인터에 0을 기록하여 매핑을 해제한다.

pte_clear()

arch/arm64/include/asm/pgtable.h

#define pte_clear(mm,addr,ptep) set_pte(ptep, __pte(0))

@ptet 엔트리 포인터에 0을 기록하여 매핑을 해제한다.

pte 엔트리 활성화 시 메모리 타입 속성

set_pte( ) 함수에서 물리 주소를 매핑할 때 메모리 타입 속성을 추가하여 매핑한 페이지에 대해 캐시 속성을 지정할 수 있다.

ARM64에서 캐시 속성은 ARM에서와 달리 단순하게 normal 메모리 타입과 device 타입을 두었다.

- Normal 타입

- 메모리 타입에 사용하고, 캐시 policy를 적용할 수 있다.

- Device 타입

- 예측 접근을 허용하지 않고, 캐시를 사용하지 않는 특징이 있다.

다음과 같은 타입의 매크로 상수 값을 사용한다.

- MT_DEVICE_nGnRnE

- ARM에서의 strongly-ordered 같은 타입으로 버퍼 및 캐시를 사용할 수 없어 디바이스에서 가장 느린 특성을 갖고 있다.

- MT_DEVICE_nGnRE

- ARM에서의 device 타입처럼 버퍼 및 캐시를 사용하지 않는다.

- MT_DEVICE_GRE

- ARMv8에서 새로 소개된 device 타입으로, 예측(predict) 접근을 허용하지 않고, 캐시를 사용하지 않는 normal 메모리와 유사하다.

- MT_NORMAL_NC

- 버퍼만 사용하고 캐시는 사용하지 않는 타입이다.

- MT_NORMAL

- MT_NORMAL_WT

- 버퍼 및 일부 기능 제한된 캐시(write-through)를 사용한다.

- MT_NORMAL_TAGGED

- MT_NORMAL과 동일하지만 MTE를 지원한다.

- 유저 페이지에서만 MTE를 지원한다.

디바이스 타입에 사용하는 세 가지 타입을 알아본다. n이 앞에 붙으면 non을 의미한다.

- G(Gather)

- 성능을 높이기 위해 다중 액세스를 병합하여 하나의 버스 트랜잭션으로 처리하는 것을 허용한다.

- 명시적으로 요청한 사이즈와 횟수만큼의 데이터 기록을 위해 버스에 전달될 때 한 번에 요청할 수 있다.

- 예) 1 바이트 문자를 이어진 주소에서 연달아 4번 기록하라고 했고, 쓰기 버퍼에서 이러한 요청을 4 바이트 워드로 병합하여 한 번에 처리한다.

- R(Reorder)

- 성능을 높이기 위해 버스를 통해 같은 디바이스에 요청될 때 프로그램 순서가 재정렬되는 것을 허용한다.

- E(Early Write Acknowledgement)

- 성능을 높이기 위해 버스에 정상 요청한 경우 응답을 기다리지 않고 다음 처리를 위해 완료한다.

- 예) 높은 신뢰성을 가진 버스와 디바이스에서 사용되는 방법이다.

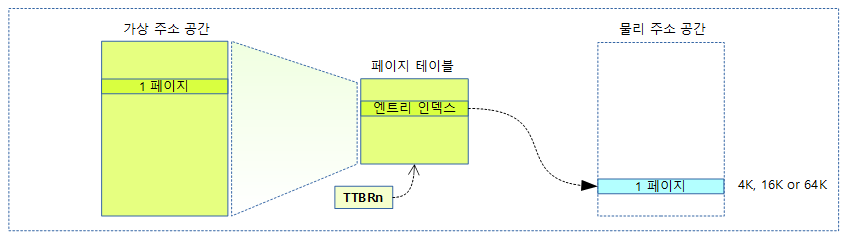

유저 공간 활성화

유저 가상 주소 공간에 해당하는 매핑을 체크하고, 매핑되지 않은 경우 유저용 메모리를 할당 후 매핑한다. 단계별로 매핑에 필요한 페이지 테이블이 추가로 필요한 경우 생성하여 연결한다.

mm_populate()

include/linux/mm.h

static inline void mm_populate(unsigned long addr, unsigned long len)

{

/* Ignore errors */

(void) __mm_populate(addr, len, 1);

}

가상 시작 주소부터 길이만큼 유저 페이지를 활성화(물리 메모리 할당)한다.

- mlocked 페이지들은 swap되지 않는 속성이 있으며 fault 핸들러에 의해 메모리를 매핑하는 lazy 할당을 사용하지 않고, 처음부터 매핑되어 사용된다.

__mm_populate()

mm/mlock.c

/*

* __mm_populate - populate and/or mlock pages within a range of address space.

*

* This is used to implement mlock() and the MAP_POPULATE / MAP_LOCKED mmap

* flags. VMAs must be already marked with the desired vm_flags, and

* mmap_lock must not be held.

*/

int __mm_populate(unsigned long start, unsigned long len, int ignore_errors)

{

struct mm_struct *mm = current->mm;

unsigned long end, nstart, nend;

struct vm_area_struct *vma = NULL;

int locked = 0;

long ret = 0;

end = start + len;

for (nstart = start; nstart < end; nstart = nend) {

/*

* We want to fault in pages for [nstart; end) address range.

* Find first corresponding VMA.

*/

if (!locked) {

locked = 1;

mmap_read_lock(mm);

vma = find_vma(mm, nstart);

} else if (nstart >= vma->vm_end)

vma = vma->vm_next;

if (!vma || vma->vm_start >= end)

break;

/*

* Set [nstart; nend) to intersection of desired address

* range with the first VMA. Also, skip undesirable VMA types.

*/

nend = min(end, vma->vm_end);

if (vma->vm_flags & (VM_IO | VM_PFNMAP))

continue;

if (nstart < vma->vm_start)

nstart = vma->vm_start;

/*

* Now fault in a range of pages. populate_vma_page_range()

* double checks the vma flags, so that it won't mlock pages

* if the vma was already munlocked.

*/

ret = populate_vma_page_range(vma, nstart, nend, &locked);

if (ret < 0) {

if (ignore_errors) {

ret = 0;

continue; /* continue at next VMA */

}

break;

}

nend = nstart + ret * PAGE_SIZE;

ret = 0;

}

if (locked)

mmap_read_unlock(mm);

return ret; /* 0 or negative error code */

}

가상 시작 주소부터 길이만큼 유저 페이지 활성(물리 메모리 할당)하고 성공하는 경우 활성화한 페이지 수를 반환한다. ignore_errors를 설정한 경우 중간 페이지가 할당 실패하여도 계속 진행한다. mlocked 페이지는 swap 되지 않는다.

- 코드 라인 9에서 가상 끝 주소를 산출한다.

- 가상 시작 주소와 길이는 페이지 단위로 정렬되어 있다.

- 코드 라인 11에서 시작 페이지부터 끝 페이지까지 루프를 돈다.

- 코드 라인 16~19에서 락이 걸리지 않은 경우 메모리 디스크립터의 mmap_read_lock을 걸고 진행 페이지가 속한 vma 영역을 알아온다.

- 코드 라인 20~21에서 요청 영역이 현재 vma 영역을 벗어난 경우 다음 vma를 준비한다.

- 코드 라인 22~23에서 요청 영역을 벗어난 vma들에 대해 더 이상 검색할 필요 없으므로 검색을 멈추고 루프를 벗어난다.

- 코드 라인 28에서 영역의 끝과 현재 vma의 끝 중 낮은 주소를 nend에 대입한다.

- 코드 라인 29~30에서 vma의 플래그에 VM_IO 또는 VM_PFNMAP이 있는 경우 skip 한다.

- 코드 라인 31~32에서 현재 진행 시작 주소가 vma의 시작 주소보다 작은 경우 진행 시작 주소를 vma 시작 주소로 대입한다.

- 코드 라인 38에서 nstart ~ nend까지의 영역에 대해 swap되지 않도록 각 페이지를 mlock 처리한다.

- 코드 라인 39~45에서 mlock 처리가 실패하는 경우 에러 코드를 가지고 루프를 탈출한다. 만일 인수 ignore_errors 가 설정된 경우 skip 한다.

- 코드 라인 46~48에서 nstart + mlock 처리된 페이지만큼 nend를 설정하고 계속 루프를 돈다.

- 코드 라인 49~51에서 락이 걸려 있는 경우 해제하고 ret를 반환한다.

참고

- ARMv8-A Memory Systems v1.0 (2017) | ARM – 다운로드 pdf