<kernel v5.4>

Common Clock Framework -1- (초기화)

CCF History

컴퓨터 하드웨어에는 많은 클럭 장치를 통해 클럭이 공급되고 있다. 시스템 내부에 cpu core에 들어가는 클럭부터 timer, i2c, uart 등 수 ~ 수십 종류의 클럭이 사용된다. 각각의 ARM SoC들은 개개의 클럭 디바이스 드라이버를 통해 클럭 설정을 하는데 하드웨어도 천차만별이고 구현된 드라이버도 기존 코드를 그대로 copy & paste를 통해 사용되고 심지어 clk 구조체 까지도 바꿔서 사용해오고 있다. 이를 해결해 보고자 CCF(Common Clock Framework)를 준비하였다. CCF는 커널 v3.4에서 처음 소개되었고 커널 v4.0에서 clk 구조체의 대부분을 clk_core 구조체로 옮겼다.

drivers/clk/clk.c를 제외하고 다음과 같이 많은 시스템에서 clk 구조체를 변경하여 사용했음을 알 수 있다. (커널 v4.0 기준)

- ccf가 소개된 이후 개발된 ARM64 아키텍처에서는 clk 구조체를 변경하여 사용한 적이 없다.

./include/linux/sh_clk.h:37:struct clk {

./drivers/clk/clk.c:80:struct clk {

./arch/c6x/include/asm/clock.h:82:struct clk {

./arch/mips/include/asm/clock.h:20:struct clk {

./arch/mips/include/asm/mach-ar7/ar7.h:147:struct clk {

./arch/mips/ralink/clk.c:19:struct clk {

./arch/mips/jz4740/clock.h:45:struct clk {

./arch/mips/ath79/clock.c:31:struct clk {

./arch/mips/lantiq/clk.h:55:struct clk {

./arch/mips/bcm63xx/clk.c:19:struct clk {

./arch/blackfin/include/asm/clocks.h:61:struct clk {

./arch/blackfin/mach-common/clock.h:14:struct clk {

./arch/arm/mach-lpc32xx/clock.h:22:struct clk {

./arch/arm/mach-w90x900/clock.h:18:struct clk {

./arch/arm/mach-sa1100/clock.c:26:struct clk {

./arch/arm/mach-davinci/clock.h:87:struct clk {

./arch/arm/mach-mmp/clock.h:18:struct clk {

./arch/arm/mach-versatile/include/mach/clkdev.h:6:struct clk {

./arch/arm/mach-pxa/clock.h:11:struct clk {

./arch/arm/mach-omap1/clock.h:141:struct clk {

./arch/arm/mach-ep93xx/clock.c:30:struct clk {

./arch/m68k/include/asm/mcfclk.h:16:struct clk {

./arch/avr32/mach-at32ap/clock.h:20:struct clk {

./arch/unicore32/kernel/clock.c:30:struct clk {

다음과 같이 커널 v5.4에서 clk 구조체를 변경하여 사용한 코드가 일부 남아 있다.

./include/linux/sh_clk.h:38:struct clk {

./drivers/clk/clk.c:97:struct clk {

./arch/unicore32/kernel/clock.c:27:struct clk {

./arch/mips/include/asm/mach-ar7/ar7.h:134:struct clk {

./arch/mips/include/asm/clock.h:21:struct clk {

./arch/mips/ralink/clk.c:18:struct clk {

./arch/mips/bcm63xx/clk.c:21:struct clk {

./arch/mips/lantiq/clk.h:58:struct clk {

./arch/m68k/include/asm/mcfclk.h:17:struct clk {

./arch/arm/mach-ep93xx/clock.c:27:struct clk {

./arch/arm/mach-omap1/clock.h:138:struct clk {

./arch/arm/mach-mmp/clock.h:12:struct clk {

./arch/c6x/include/asm/clock.h:79:struct clk {

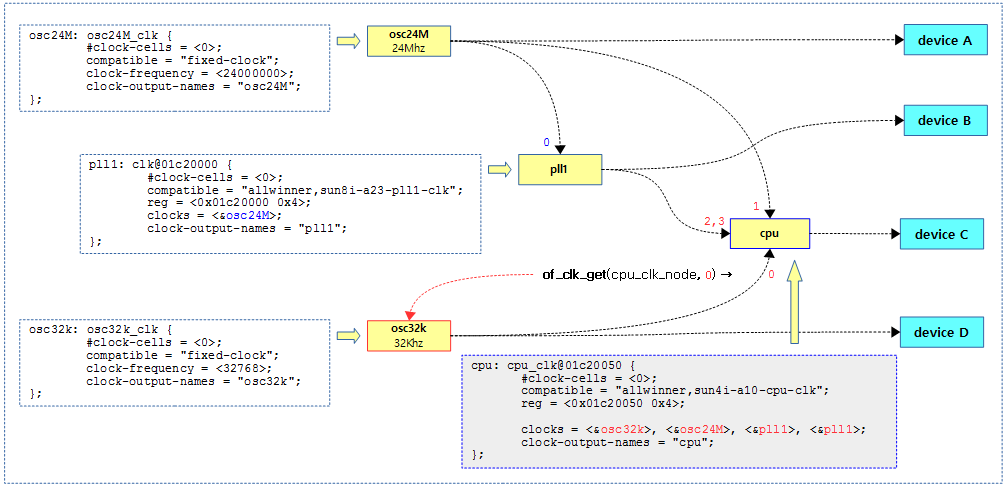

클럭 Diagram

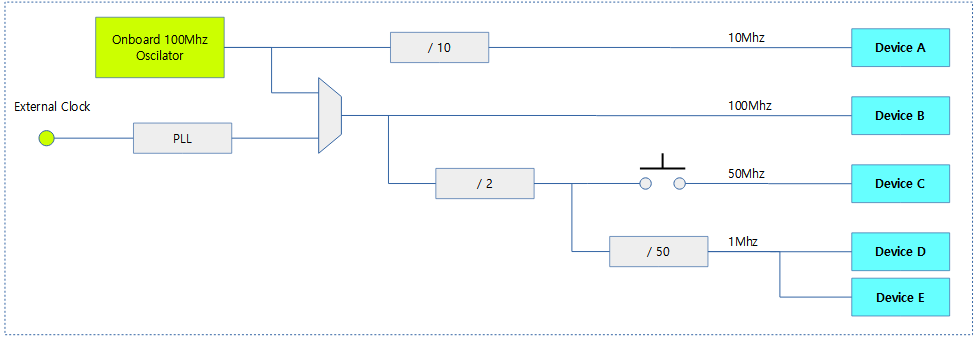

다음 그림은 클럭 다이어그램 샘플을 보여준다.

- Device A는 onboard 클럭을 10으로 분주(divide)한 클럭 rate를 공급받는다.

- Devce B~E가 external 클럭을 공급받는 경우 PLL 설정이 필요하다.

클럭 Provider & Consumer

클럭을 공급하는 장치인 Clock Provider와 클럭을 가져다 사용하는 Clock Consumer의 특징을 알아본다.

클럭 Provider

- CCF 기반의 클럭 디바이스 드라이버를 통해 구현된다.

- common CCF를 사용하면 유사한 기능을 갖는 클럭 디바이스를 간단히 개발할 수 있다.

- 클럭 rate, 분주 값 및 Multiplexer의 선택은 디바이스 트리를 통해 각각의 보드 상황에 맞게 설정할 수 있다.

클럭 Consumer

- 디바이스 트리를 통해 사용할 클럭을 지정하여 사용할 수 있다.

- 런타임에 수동으로 멀티플렉서나 Gate의 제어가 필요한 경우 클럭 API들을 통해서 제어할 수 있다.

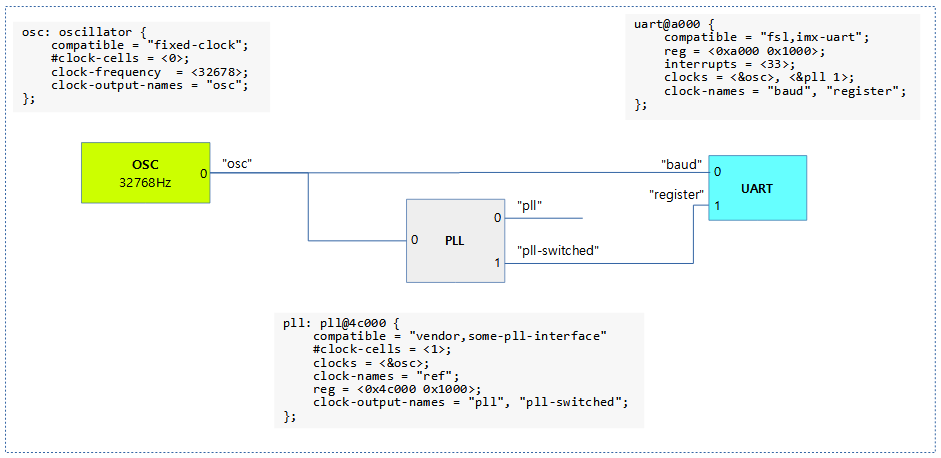

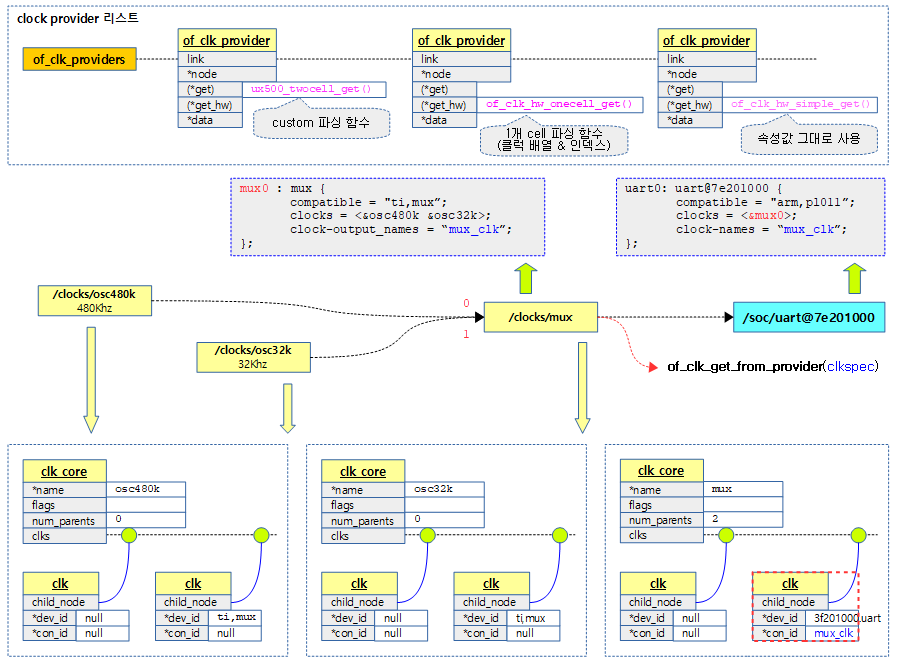

다음 그림은 기본적인 Clock Provider와 Clock Consumer의 관계와 디바이스 트리에서의 표현을 보여준다.

- OSC가 Clock Provider로 사용되었고, PLL이 Clock Consumer이자 Clock Provider로 사용된다.

- UART는 Clock Consumer로 사용된다.

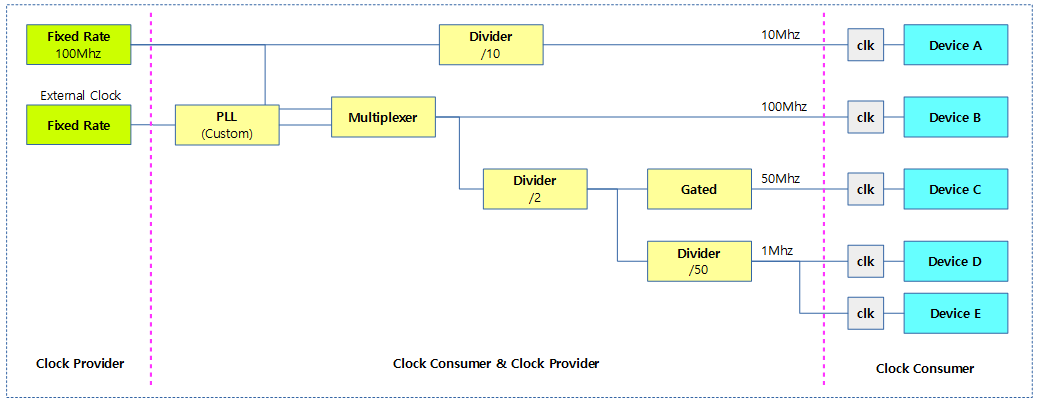

다음 그림은 Clock Provider와 Clock Consumer들을 보여준다.

- PLL의 경우 별도의 custom 드라이버를 통해 구현되는데, 여러 가지 CCF 타입이 혼재되어 구현된다.

- 노란색 클럭들은 상위 Clock에 대한 Clock Consumer이면서 하위 디바이스에 대한 Clock Provider를 수행한다.

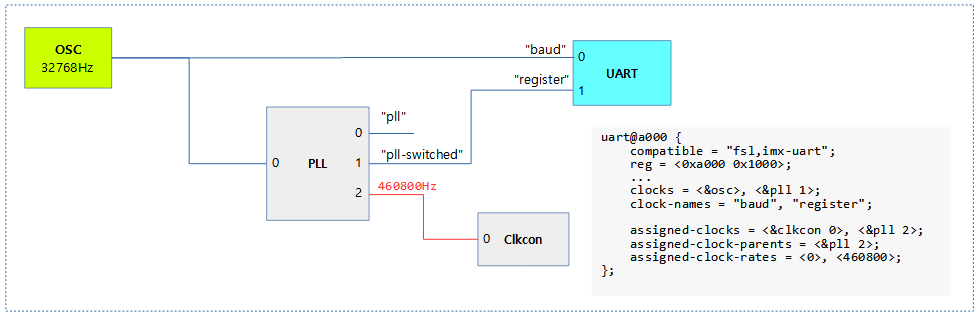

Assigned-clock

몇가지 플랫폼에서는 다음과 같이 clock provider의 rate 설정 또는 mux(parent) 입력 소스 선택을 지원하는 속성을 제공한다.

- assigned-clocks =

- assigned-clock-parents =

- assigned-clock-rates =

다음 그림은 clkcon 0의 입력 소스로 pll 2를 선택하게하고, pll 2의 rate를 460800hz로 지정하도록 하는 모습을 보여준다.

CCF 구조

drivers/clk 디렉토리를 살펴보면 수 백 개의 클럭 관련 디바이스 파일이 존재한다.

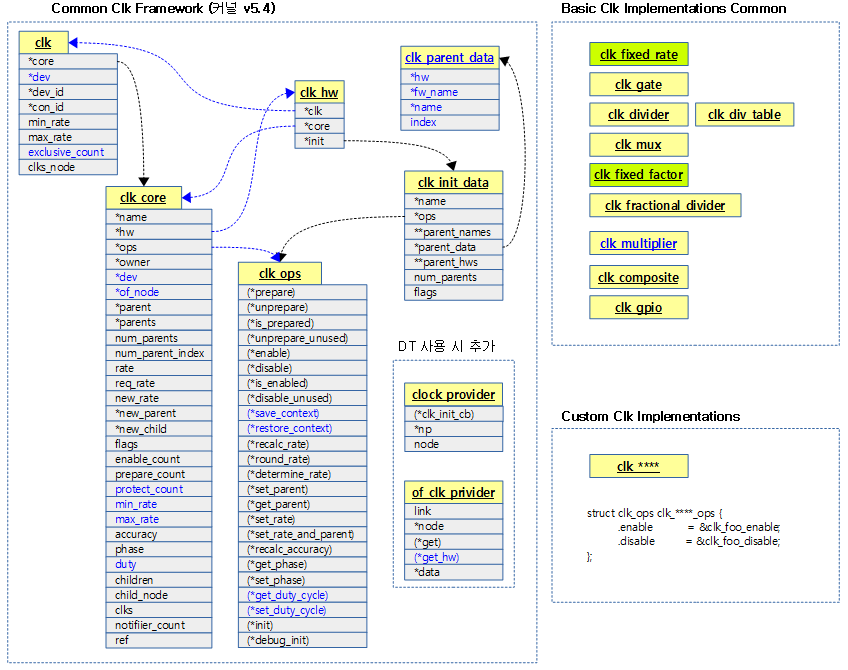

common clock framework에서 사용하는 구조체는 다음과 같다.

- struct clk_core

- 클럭 제공자(provider)로 고정 클럭을 포함하여 Rate, Mux, Gate 타입 등 여러 종류의 클럭 클럭을 포함한다.

- struct clk

- 클럭 사용자(consumer)로 사용할 clk_core에 연결된다.

- 예외 사항으로 클럭 consumer가 아니지만 clk_core 생성 시에 따라 생성되는 clk도 있다. 이들의 용도는 clk_core가 삭제되지 않도록 참조한다.

- 처음 소개된 CCF에서는 부모 관계 설정도 하였지만, 이러한 관계 설정은 clk_core로 이전되었다.

- struct clk_hw

- 클럭 hw는 클럭 core와 클럭을 연결한다.

- struct clk_ops

- 클럭 코어가 동작하는 여러 가지 후크를 가진다.

- struct clk_init_data

- 클럭 코어를 초기화할 때 사용하는 데이터가 담긴다.

- struct clk_parent_data

- 부모 클럭 코어와 연결될 때 사용된다.

- 참고: clk: Allow parents to be specified without string names (2019, v5.2-rc1)

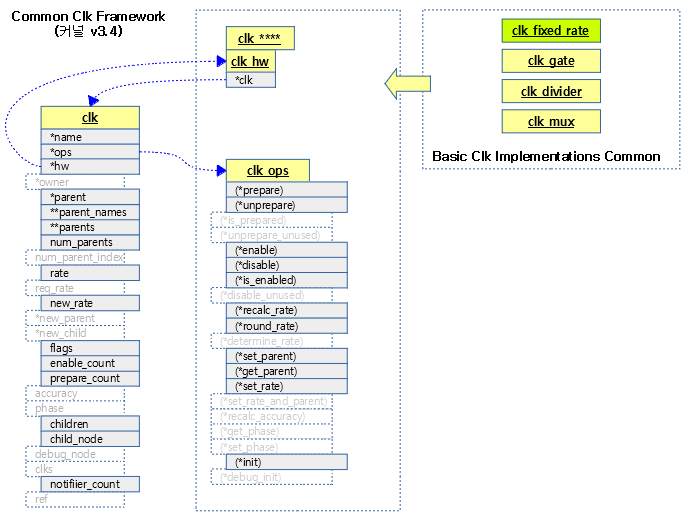

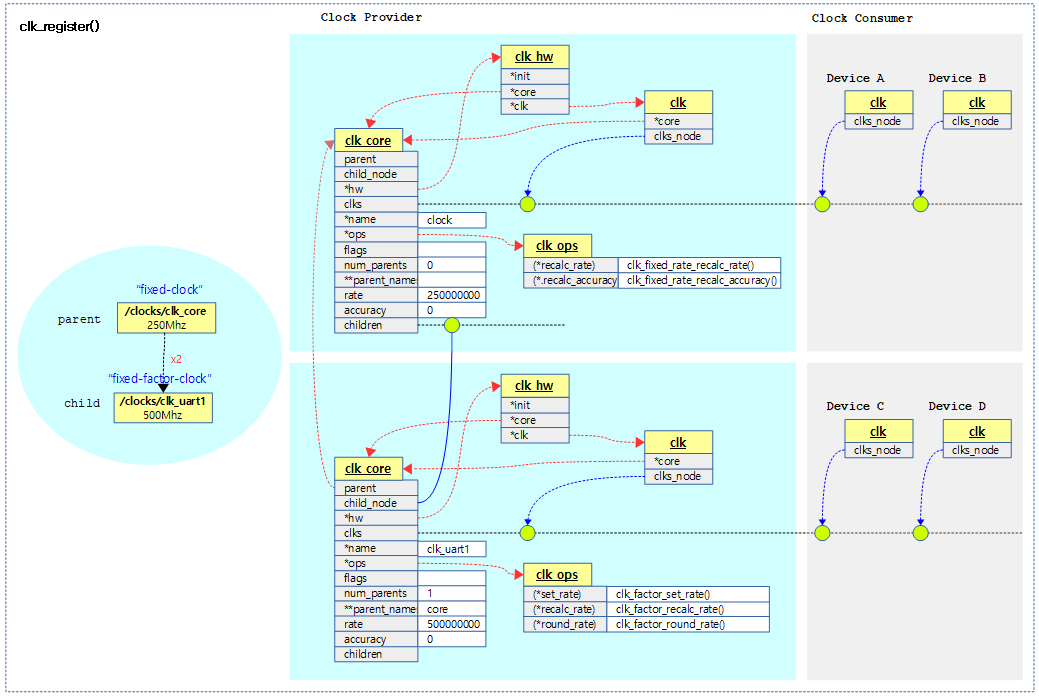

다음 그림에서 provider로 사용된 clk 구조체와 consumer로 사용된 clk 구조체를 비교해본다.

다음 그림은 최근 커널의 Common Clk Framework를 보여준다.

- 파란색 글씨는 커널 v4.0으로부터 추가된 항목들이다.

다음 그림은 Common Clk Framework이 소개되었을 당시의 모습을 보여준다.

구현된 기본 공통 클럭 타입

Basic clock implementations common

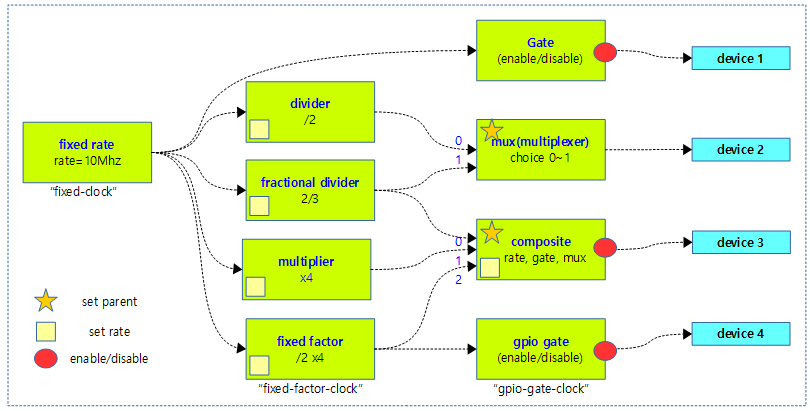

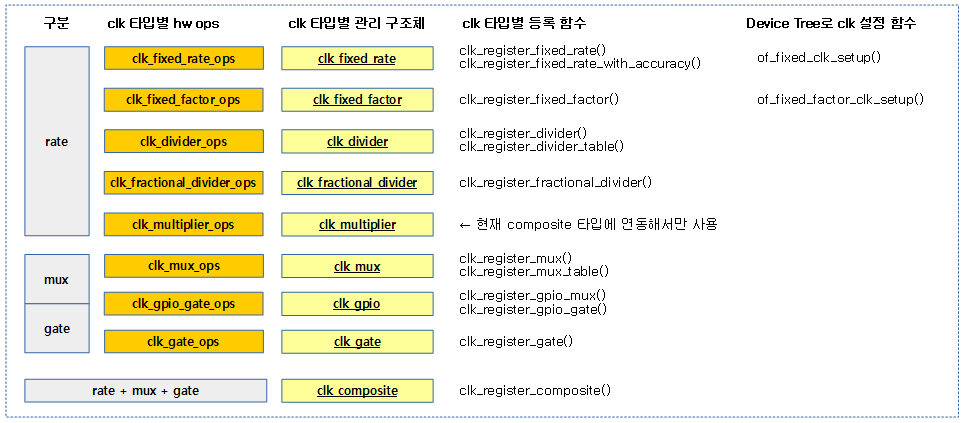

가장 많이 사용할 수 있는 공통 기본 클럭 구현이 다음과 같이 9개가 준비되어 있다. 공통 기본 클럭 구현만으로 구성 할 수 없는 시스템은 더 확장하여 구성할 수도 있다.

Rate 클럭들

Fixed rate 및 Fixed factor 타입 클럭을 제외하고 각자 hw를 제어하기 위해 custom 클럭 디바이스 드라이버가 구현되어야 한다.

- Fixed rate clock 구현

- 고정된 rate와 정밀도(accuracy)로 동작하고 gate는 제어할 수 없다.

- compatible

- rate를 조절하는 컨트롤 기능이 없는 경우 이 common 드라이버를 사용한다.

- “fixed-clock“

- Fixed Factor(multiplier and divider) clock 구현

- 배율기 및 분배기로 동작하여 rate를 설정하고 gate는 제어할 수 없다.

- rate = 고정된 부모 clock의 rate / 분배값(div) * 배율값(mult)

- compatible

- 배율을 조절하는 컨트롤 기능이 없는 경우 이 common 드라이버를 사용한다.

- “fixed-factor-clock“

- divider clock 구현

- 분배기로 rate가 설정되고 gate는 제어할 수 없다.

- rate = 고정된 부모 clock의 rate / 분배값(div)

- compatible

- 실제 분배율을 hw로 제어해야 하기 때문에 각 클럭 컨트롤러 제조사의 레지스터 주소를 등록하여 사용하도록 각사의 디바이스 드라이버를 사용한다.

- 예) “ti,divider-clock”

- Fractional divider clock 구현

- 분수 분배기로 rate를 설정하고 gate는 제어할 수 없다.

- rate = 고정된 부모 clock의 rate * 분수(fractional)

- compatible

- 실제 분수 분배율을 hw로 제어해야 하기 때문에 각 클럭 컨트롤러 제조사의 레지스터를 컨트롤하는 각사의 디바이스 드라이버를 사용한다.

- Multiplier clock 구현

- 배율기로 동작한다.

- rate = 고정된 부모 clock의 rate * mult

- compatible

- 동작에 따른 조작을 hw로 제어해야 하기 때문에 각 클럭 컨트롤러 제조사의 레지스터를 컨트롤하는 각사의 디바이스 드라이버를 사용한다.

- 예) “allwinner,sun4i-a10-pll3-clk”

- 참고: clk: Add a basic multiplier clock (2015, v4.4-rc1)

Mux 클럭들

각자 hw를 제어하기 위해 custom 클럭 디바이스 드라이버가 구현되어야 한다.

- Simple multiplexer clock 구현

- 간단한 멀티플렉서로 동작하여 dynamic하게 부모 클럭을 선택할 수 있고 gate는 제어할 수 없다.

- compatible

- 실제 입력 소스를 hw로 선택해야 하기 때문에 각 클럭 컨트롤러 제조사의 레지스터를 컨트롤하는 각사의 디바이스 드라이버를 사용한다.

- 예) “ti,mux-clock”

Gate 클럭들

Gpio gated 타입 클럭은 common gpio 디바이스 드라이버를 통해 hw를 제외하므로 별도의 클럭 디바이스 드라이버의 구현이 필요 없고, 그 외의 gated 타입 클럭은 hw를 제어하기 위해 custom 클럭 디바이스 드라이버가 구현되어야 한다.

- Gpio gated clock 구현

- gpio를 사용하여 gate를 제어한다.

- rate는 직접 지정할 수 없고 고정(fixed)된 부모로부터 rate는 상속받아야 한다.

- compatible

- gate의 hw 조작을 common gpio 드라이버를 통해서 동작하므로 별도의 custome 디바이스 드라이버 제작없이 이 타입의 디바이스 드라이버를 사용한다.

- “gpio-gate-clock“

- Gated clock 구현

- gate를 제어 할 수 있다.

- rate는 직접 지정할 수 없고 고정(fixed)된 부모 clock으로부터 rate는 상속받아야 한다.

- compatible

- 실제 gate를 hw 제어해야하기 때문에 각 클럭 컨틀롤러 제조사의 레지스터를 컨트롤하는 각자의 디바이스 드라이버 필요하다.

- 예) ti,gate-clock”

Composite 클럭들

- Composite clock 구현

- rate, mux(multiplexer) 및 gate 클럭들의 기능을 동시에 복합 구성하여 동작한다.

- compatible

- 복합 동작에 따른 조작을 hw 제어해야 하기 때문에 각 클럭 컨트롤러 제조사의 레지스터를 컨트롤하는 각사의 디바이스 드라이버를 사용한다.

- 예) “ti,composite-clock”

클럭 하드웨어 도면은 아래 사이트를 참고한다.

- 클럭 신호 | 위키백과

- TMS320C674x 소개-주변장치(3)

- [TMS320F28377D] Data Manual – Feature : Clock | MCU Blog

다음 그림은 9개의 클럭 디바이스 사용 예를 각각 보여준다.

다음 그림은 common 클럭 타입별 커스텀 드라이버가 제어를 해야할 레지스터 부분을 보여준다.

- 아래 하늘색 박스와 같이 gpio gate 클럭 드라이버는 common gpio 드라이버를 사용하여 제어한다.

- 9개의 common 클럭 구현이 준비되어 있다.

- 3개의 공통 클럭 디바이스 드라이버는 device tree로 설정 가능하며 완성된 형태로 사용된다.

- 나머지 6개는 custom 클럭 디바이스 드라이버를 통해 쉽게 구현이 가능하다. (ti, samsung, etc…)

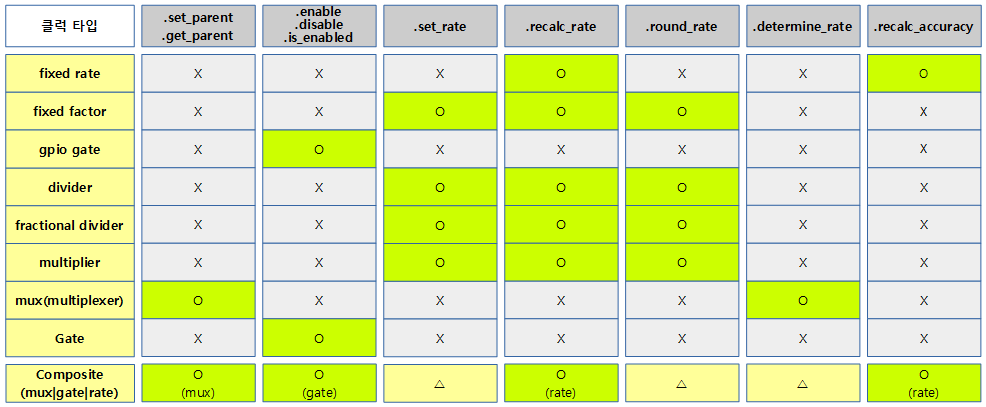

다음 그림은 common 클럭 타입별 사용되는 ops 콜백 함수를 보여준다.

Device Tree 지원

클럭 디바이스 드라이버도 머신 형태의 각 개별 custom 드라이버를 사용하지 않고 점차 Device Tree를 지원하는 형태로 바뀌어 가고 있다. 즉 런타임에 Device Tree Blob 내용을 파싱하여 시스템에 맞게 클럭을 설정하는 형태이므로 모든 설정방법이 Device Tree Script에 표현되어 있어야 한다.

다음의 추가 구조체를 사용한다.

- clock_provider

- of_clk_provider

심플한 구현

common 클럭들을 사용하는 경우 hw 조작을 위해 관련 레지스터 주소와 함께 클럭을 등록하여 간단하게 디바이스 트리용 클럭 드라이버를 만들 수 있다. 다음 예는 가장 간단히 만들 수 있는 실제 divider 클럭 드라이버 코드를 보여준다.

drivers/clk/h8300/clk-div.c

#include <linux/clk-provider.h>

#include <linux/err.h>

#include <linux/io.h>

#include <linux/of.h>

#include <linux/of_address.h>

static DEFINE_SPINLOCK(clklock);

static void __init h8300_div_clk_setup(struct device_node *node)

{

unsigned int num_parents;

struct clk_hw *hw;

const char *clk_name = node->name;

const char *parent_name;

void __iomem *divcr = NULL;

int width;

int offset;

num_parents = of_clk_get_parent_count(node);

if (!num_parents) {

pr_err("%s: no parent found\n", clk_name);

return;

}

divcr = of_iomap(node, 0);

if (divcr == NULL) {

pr_err("%s: failed to map divide register\n", clk_name);

goto error;

}

offset = (unsigned long)divcr & 3;

offset = (3 - offset) * 8;

divcr = (void __iomem *)((unsigned long)divcr & ~3);

parent_name = of_clk_get_parent_name(node, 0);

of_property_read_u32(node, "renesas,width", &width);

hw = clk_hw_register_divider(NULL, clk_name, parent_name,

CLK_SET_RATE_GATE, divcr, offset, width,

CLK_DIVIDER_POWER_OF_TWO, &clklock);

if (!IS_ERR(hw)) {

of_clk_add_hw_provider(node, of_clk_hw_simple_get, hw);

return;

}

pr_err("%s: failed to register %s div clock (%ld)\n",

__func__, clk_name, PTR_ERR(hw));

error:

if (divcr)

iounmap(divcr);

}

CLK_OF_DECLARE(h8300_div_clk, "renesas,h8300-div-clock", h8300_div_clk_setup);

2의 배수 단계로 나누는 divider 클럭이다.

- n 비트 셀렉터 값

- (레지스터(reg) 값 >> offset) & width

- width=2인 경우 2 bit 셀렉터를 사용하여 4단계(1/1, 1/2, 1/4, 1/8)로 클럭 rate를 나눌 수 있다.

다음은 위 클럭 디바이스 드라이버를 사용하는 4단계 divier 클럭 디바이스를 정의한 디바이스 트리 설정이다. (core_clk 부분)

arch/h8300/boot/dts/h8300h_sim.dts

...

xclk: oscillator {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <20000000>;

clock-output-names = "xtal";

};

core_clk: core_clk {

compatible = "renesas,h8300-div-clock";

clocks = <&xclk>;

#clock-cells = <0>;

reg = <0xfee01b 2>;

renesas,width = <2>;

};

fclk: fclk {

compatible = "fixed-factor-clock";

clocks = <&core_clk>;

#clock-cells = <0>;

clock-div = <1>;

clock-mult = <1>;

};

...

20Mhz 고정 클럭 -> 4 단계 divider -> 1/1 Factor 클럭 순으로 클럭이 공급됨을 알 수 있다.

DEBUGFS 관리

Device Tree로 부팅한 rpi2에서 등록된 7개의 클럭을 다음의 디렉토리를 통해 살펴볼 수 있다.

# cd /sys/kernel/debug/clk

# ls -l

total 0

drwxr-xr-x 2 root root 0 Jan 1 1970 apb_pclk

-r--r--r-- 1 root root 0 Jan 1 1970 clk_dump

-r--r--r-- 1 root root 0 Jan 1 1970 clk_orphan_dump

-r--r--r-- 1 root root 0 Jan 1 1970 clk_orphan_summary

-r--r--r-- 1 root root 0 Jan 1 1970 clk_summary

drwxr-xr-x 2 root root 0 Jan 1 1970 clock

drwxr-xr-x 2 root root 0 Jan 1 1970 core

drwxr-xr-x 2 root root 0 Jan 1 1970 mmc

drwxr-xr-x 2 root root 0 Jan 1 1970 osc

drwxr-xr-x 2 root root 0 Jan 1 1970 pwm

drwxr-xr-x 2 root root 0 Jan 1 1970 uart0_pclk

# cat clk_summary

clock enable_cnt prepare_cnt rate accuracy phase

----------------------------------------------------------------------------------------

osc 0 0 19200000 0 0

pwm 0 0 100000000 0 0

apb_pclk 1 1 126000000 0 0

uart0_pclk 1 1 48000000 0 0

mmc 0 0 250000000 0 0

core 0 0 400000000 0 0

clock 0 0 800000000 0 0

다음은 rpi4(Ubuntu 4.18.03)에서 사용된 클럭들을 보여준다. (커널 v4.19)

$ cd /sys/kernel/debug/clk

rpi4 /sys/kernel/debug/clk$ ls -l

total 0

drwxr-xr-x 2 root root 0 Jan 1 1970 aux_spi1

drwxr-xr-x 2 root root 0 Jan 1 1970 aux_spi2

drwxr-xr-x 2 root root 0 Jan 1 1970 aux_uart

drwxr-xr-x 2 root root 0 Jan 1 1970 aveo

drwxr-xr-x 2 root root 0 Jan 1 1970 cam0

drwxr-xr-x 2 root root 0 Jan 1 1970 cam1

-r--r--r-- 1 root root 0 Jan 1 1970 clk_dump

-r--r--r-- 1 root root 0 Jan 1 1970 clk_orphan_dump

-r--r--r-- 1 root root 0 Jan 1 1970 clk_orphan_summary

-r--r--r-- 1 root root 0 Jan 1 1970 clk_summary

drwxr-xr-x 2 root root 0 Jan 1 1970 dft

drwxr-xr-x 2 root root 0 Jan 1 1970 dpi

drwxr-xr-x 2 root root 0 Jan 1 1970 dsi0e

drwxr-xr-x 2 root root 0 Jan 1 1970 dsi0p

drwxr-xr-x 2 root root 0 Jan 1 1970 dsi1e

drwxr-xr-x 2 root root 0 Jan 1 1970 dsi1p

drwxr-xr-x 2 root root 0 Jan 1 1970 emmc

drwxr-xr-x 2 root root 0 Jan 1 1970 emmc2

drwxr-xr-x 2 root root 0 Jan 1 1970 gp0

drwxr-xr-x 2 root root 0 Jan 1 1970 gp1

drwxr-xr-x 2 root root 0 Jan 1 1970 gp2

drwxr-xr-x 2 root root 0 Jan 1 1970 h264

drwxr-xr-x 2 root root 0 Jan 1 1970 hsm

drwxr-xr-x 2 root root 0 Jan 1 1970 isp

drwxr-xr-x 2 root root 0 Jan 1 1970 osc

drwxr-xr-x 2 root root 0 Jan 1 1970 otg

drwxr-xr-x 2 root root 0 Jan 1 1970 otp

drwxr-xr-x 2 root root 0 Jan 1 1970 pcm

drwxr-xr-x 2 root root 0 Jan 1 1970 peri_image

drwxr-xr-x 2 root root 0 Jan 1 1970 plla

drwxr-xr-x 2 root root 0 Jan 1 1970 plla_ccp2

drwxr-xr-x 2 root root 0 Jan 1 1970 plla_core

drwxr-xr-x 2 root root 0 Jan 1 1970 plla_dsi0

drwxr-xr-x 2 root root 0 Jan 1 1970 plla_per

drwxr-xr-x 2 root root 0 Jan 1 1970 pllb

drwxr-xr-x 2 root root 0 Jan 1 1970 pllb_arm

drwxr-xr-x 2 root root 0 Jan 1 1970 pllc

drwxr-xr-x 2 root root 0 Jan 1 1970 pllc_core0

drwxr-xr-x 2 root root 0 Jan 1 1970 pllc_core1

drwxr-xr-x 2 root root 0 Jan 1 1970 pllc_core2

drwxr-xr-x 2 root root 0 Jan 1 1970 pllc_per

drwxr-xr-x 2 root root 0 Jan 1 1970 plld

drwxr-xr-x 2 root root 0 Jan 1 1970 plld_core

drwxr-xr-x 2 root root 0 Jan 1 1970 plld_dsi0

drwxr-xr-x 2 root root 0 Jan 1 1970 plld_dsi1

drwxr-xr-x 2 root root 0 Jan 1 1970 plld_per

drwxr-xr-x 2 root root 0 Jan 1 1970 pwm

drwxr-xr-x 2 root root 0 Jan 1 1970 sdram

drwxr-xr-x 2 root root 0 Jan 1 1970 slim

drwxr-xr-x 2 root root 0 Jan 1 1970 smi

drwxr-xr-x 2 root root 0 Jan 1 1970 tec

drwxr-xr-x 2 root root 0 Jan 1 1970 timer

drwxr-xr-x 2 root root 0 Jan 1 1970 tsens

drwxr-xr-x 2 root root 0 Jan 1 1970 uart

drwxr-xr-x 2 root root 0 Jan 1 1970 v3d

drwxr-xr-x 2 root root 0 Jan 1 1970 vec

drwxr-xr-x 2 root root 0 Jan 1 1970 vpu

rpi4 /sys/kernel/debug/clk$ cat clk_summary

enable prepare protect duty

clock count count count rate accuracy phase cycle

---------------------------------------------------------------------------------------------

otg 0 0 0 480000000 0 0 50000

osc 5 5 0 54000000 0 0 50000

tsens 1 1 0 3375000 0 0 50000

otp 0 0 0 13500000 0 0 50000

timer 0 0 0 1000000 0 0 50000

plld 5 5 0 2999999988 0 0 50000

plld_dsi1 1 1 0 11718750 0 0 50000

plld_dsi0 1 1 0 11718750 0 0 50000

plld_per 3 3 0 749999997 0 0 50000

emmc2 1 1 0 99999999 0 0 50000

uart 1 1 0 47999999 0 0 50000

plld_core 1 1 0 599999998 0 0 50000

pllc 5 5 0 2999999988 0 0 50000

pllc_per 1 1 0 599999998 0 0 50000

emmc 0 0 0 199999999 0 0 50000

pllc_core2 1 1 0 11718750 0 0 50000

pllc_core1 1 1 0 11718750 0 0 50000

pllc_core0 2 2 0 499999998 0 0 50000

vpu 2 2 0 500000000 0 0 50000

aux_spi2 0 0 0 500000000 0 0 50000

aux_spi1 0 0 0 500000000 0 0 50000

aux_uart 0 0 0 500000000 0 0 50000

peri_image 0 0 0 500000000 0 0 50000

pllb 2 2 0 2999999988 0 0 50000

pllb_arm 1 1 0 1499999994 0 0 50000

plla 2 2 0 2999999988 0 0 50000

plla_ccp2 0 0 0 11718750 0 0 50000

plla_dsi0 0 0 0 11718750 0 0 50000

plla_per 0 0 0 11718750 0 0 50000

plla_core 2 2 0 499999998 0 0 50000

h264 0 0 0 499999998 0 0 50000

isp 0 0 0 499999998 0 0 50000

v3d 1 1 0 31257631 0 0 50000

dsi1p 0 0 0 0 0 0 50000

dsi0p 0 0 0 0 0 0 50000

dsi1e 0 0 0 0 0 0 50000

dsi0e 0 0 0 0 0 0 50000

cam1 0 0 0 0 0 0 50000

cam0 0 0 0 0 0 0 50000

dpi 0 0 0 0 0 0 50000

tec 0 0 0 0 0 0 50000

smi 0 0 0 0 0 0 50000

slim 0 0 0 0 0 0 50000

gp2 0 0 0 0 0 0 50000

gp1 0 0 0 0 0 0 50000

gp0 0 0 0 0 0 0 50000

dft 0 0 0 0 0 0 50000

aveo 0 0 0 0 0 0 50000

pcm 0 0 0 0 0 0 50000

pwm 0 0 0 0 0 0 50000

sdram 0 0 0 0 0 0 50000

hsm 0 0 0 0 0 0 50000

vec 0 0 0 0 0 0 50000

Device Tree로 Clk 초기화

of_clk_init()

drivers/clk/clk.c

/** * of_clk_init() - Scan and init clock providers from the DT * @matches: array of compatible values and init functions for providers. * * This function scans the device tree for matching clock providers * and calls their initialization functions. It also does it by trying * to follow the dependencies. */

void __init of_clk_init(const struct of_device_id *matches)

{

const struct of_device_id *match;

struct device_node *np;

struct clock_provider *clk_provider, *next;

bool is_init_done;

bool force = false;

LIST_HEAD(clk_provider_list);

if (!matches)

matches = &__clk_of_table;

/* First prepare the list of the clocks providers */

for_each_matching_node_and_match(np, matches, &match) {

struct clock_provider *parent;

if (!of_device_is_available(np))

continue;

parent = kzalloc(sizeof(*parent), GFP_KERNEL);

if (!parent) {

list_for_each_entry_safe(clk_provider, next,

&clk_provider_list, node) {

list_del(&clk_provider->node);

of_node_put(clk_provider->np);

kfree(clk_provider);

}

of_node_put(np);

return;

}

parent->clk_init_cb = match->data;

parent->np = of_node_get(np);

list_add_tail(&parent->node, &clk_provider_list);

}

while (!list_empty(&clk_provider_list)) {

is_init_done = false;

list_for_each_entry_safe(clk_provider, next,

&clk_provider_list, node) {

if (force || parent_ready(clk_provider->np)) {

/* Don't populate platform devices */

of_node_set_flag(clk_provider->np,

OF_POPULATED);

clk_provider->clk_init_cb(clk_provider->np);

of_clk_set_defaults(clk_provider->np, true);

list_del(&clk_provider->node);

of_node_put(clk_provider->np);

kfree(clk_provider);

is_init_done = true;

}

}

/*

* We didn't manage to initialize any of the

* remaining providers during the last loop, so now we

* initialize all the remaining ones unconditionally

* in case the clock parent was not mandatory

*/

if (!is_init_done)

force = true;

}

}

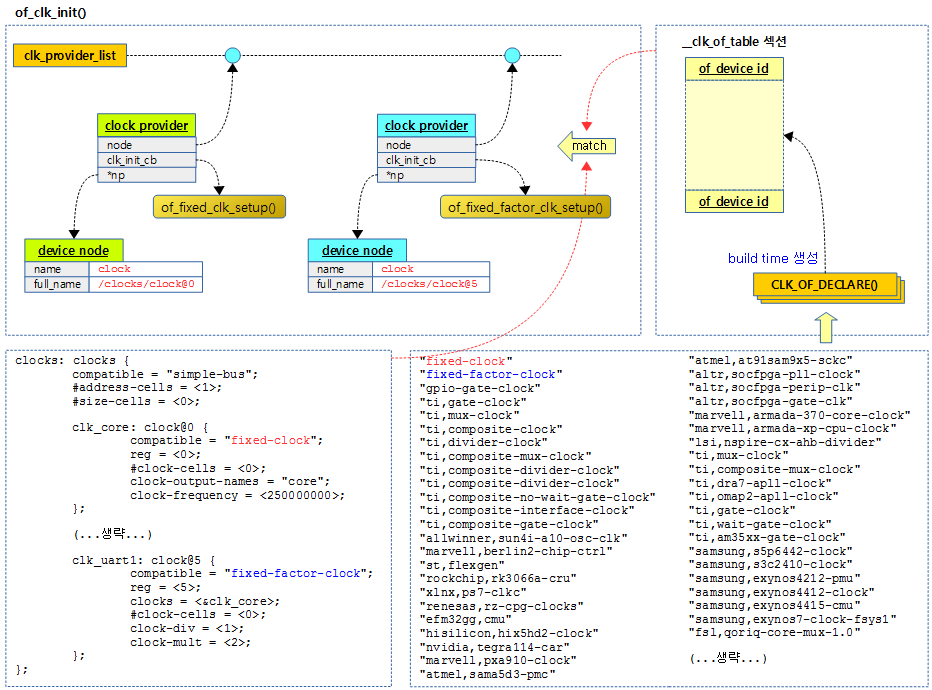

Device Tree에서 clock provider를 스캔하고 초기화한다.

- 코드 라인 10~11에서 matches 값으로 null이 지정된 경우 컴파일 타임에 CLK_OF_DECLARE() 매크로로 만들어진 __clk_of_table 섹션에 있는 모든 클럭 엔트리를 대상으로 한다.

- 코드 라인 14~35에서 Device Tree에서 matches와 엔트리와 비교하여 일치하는 항목들에 대해 루프를 돌며 clock_provider를 할당받아 구성하고 clk_provider_list에 추가한다. 메모리 부족 시에는 등록된 모든 clock_provider를 할당 해제하고함수를 빠져나간다.

- clk_init_cb에는 클럭 초기화 함수가 대입된다.

- np에는 device_node가 대입된다.

- 코드 라인 37~38에서 clk_provider_list의 엔트리가 비워질때 까지 루프를 돈다. is_init_done을 false로 하여 다음 루프에서 초기화함수를 한 번도 호출하지 않은 경우 다음에 루프를 돌면 강제로 호출하게 만든다.

- 코드 라인 39~40에서 clk_provide_list의 엔트리 수 만큼 루프를 돈다.

- 코드 라인 41~54에서 이전 루프에서 한 번도 초기화 함수를 호출하지 않은 경우와 부모 클럭이 없거나 모두 초기화된 경우 해당 클럭의 초기화 함수를 호출하고 이 클럭을 default로 설정한다. 그런 후 clk_provider_list에서 제거하고 루프내에서 한 번이라도 초기화되었음을 알리도록 is_int_done을 true로 설정한다.

- 코드 라인 63~64에서 이 전 루프를 돌 때 한 번도 초기화된 적 없으면 force를 true로 하여 다시 한 번 루프를 돌 때 남은 나머지 클럭을 무조건 초기화 처리하도록 한다.

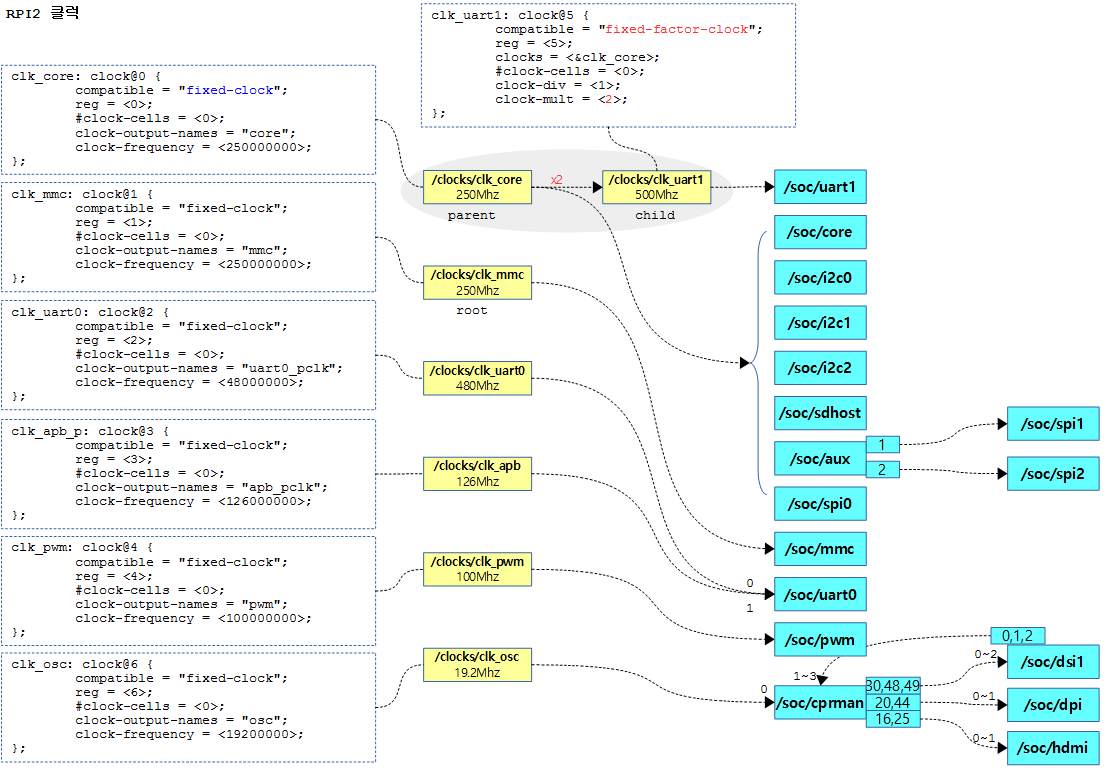

다음 그림에서와 같이 rpi2는 clock@0 ~ clock@6 까지 총 7개의 clock을 사용하며 이에 대한 각각의 초기화 함수가 호출되는 것을 보여준다.

- clock@0~4, 6의 6개의 클럭은 “fixed-clock” 디바이스 드라이버에서 구현된 fixed rate clock 타입으로 of_fixed_clk_setup() 함수를 호출한다.

- clock@5를 사용하는 1 개의 uart 클럭은 “fixed-factor-clock” 디바이스 드라이버에서 구현된 Fixed multiplier and divider clock 타입으로 of_fixed_factor_clk_setup() 함수를 호출한다.

- 이 클럭의 부모 클럭인 core clock에서 사용하는 rate 값인 250Mhz를 2배 곱하여(multiplex) 500Mhz로 uart clock의 rate로 동작시킨다.

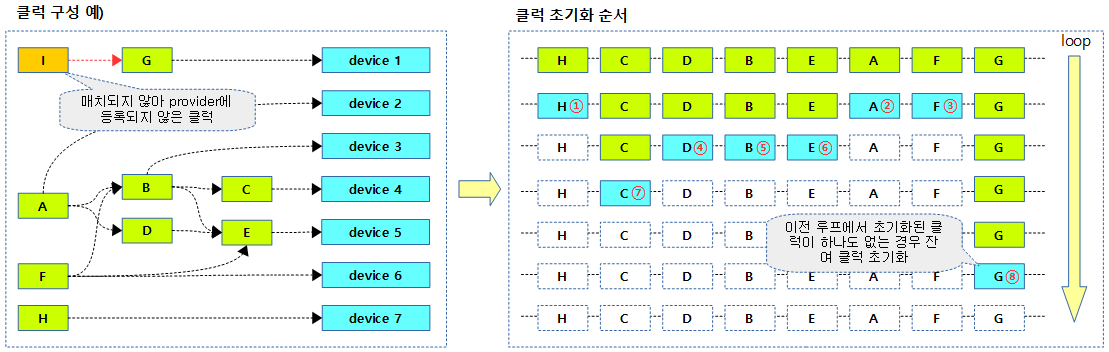

다음 그림은 좌측의 A~I 까지의 클럭 디바이스 구성에 대해 부모(parent) 클럭 디바이스부터 초기화되는 과정을 보여준다.

- 리스트에 H, C, D, B, E, A, F, G 클럭 프로바이더들이 등록되어 있다고 가정한다.

parent_ready()

drivers/clk/clk.c

/* * This function looks for a parent clock. If there is one, then it * checks that the provider for this parent clock was initialized, in * this case the parent clock will be ready. */

static int parent_ready(struct device_node *np)

{

int i = 0;

while (true) {

struct clk *clk = of_clk_get(np, i);

/* this parent is ready we can check the next one */

if (!IS_ERR(clk)) {

clk_put(clk);

i++;

continue;

}

/* at least one parent is not ready, we exit now */

if (PTR_ERR(clk) == -EPROBE_DEFER)

return 0;

/*

* Here we make assumption that the device tree is

* written correctly. So an error means that there is

* no more parent. As we didn't exit yet, then the

* previous parent are ready. If there is no clock

* parent, no need to wait for them, then we can

* consider their absence as being ready

*/

return 1;

}

}

요청한 클럭 노드의 부모 클럭 노드들 모두가 초기화 되었는지 여부를 알아온다. 1=부모 클럭 노드가 없거나 모두 초기화 된 경우, 0=부모 클럭 노드들 중 하나라도 초기화 되지 않았을 경우

- 코드 라인 5~6에서 클럭의 부모 노드가 여러 개일 수 있으므로 루프를 반복하고 지정한 인덱스의 부모 클럭을 알아온다.

- 코드 라인 9~13에서 지정된 인덱스의 부모 클럭이 이미 초기화된 경우 인덱스를 증가시키고 skip 한다.

- 코드 라인 16~17에서 부모 클럭 노드가 아직 초기화되지 않은 경우 0을 반환한다.

- 코드 라인 27에서 부모가 없는 경우 1을 반환한다.

clk 검색 -1-

clk_core_lookup()

drivers/clk/clk.c

static struct clk_core *clk_core_lookup(const char *name)

{

struct clk_core *root_clk;

struct clk_core *ret;

if (!name)

return NULL;

/* search the 'proper' clk tree first */

hlist_for_each_entry(root_clk, &clk_root_list, child_node) {

ret = __clk_lookup_subtree(name, root_clk);

if (ret)

return ret;

}

/* if not found, then search the orphan tree */

hlist_for_each_entry(root_clk, &clk_orphan_list, child_node) {

ret = __clk_lookup_subtree(name, root_clk);

if (ret)

return ret;

}

return NULL;

}

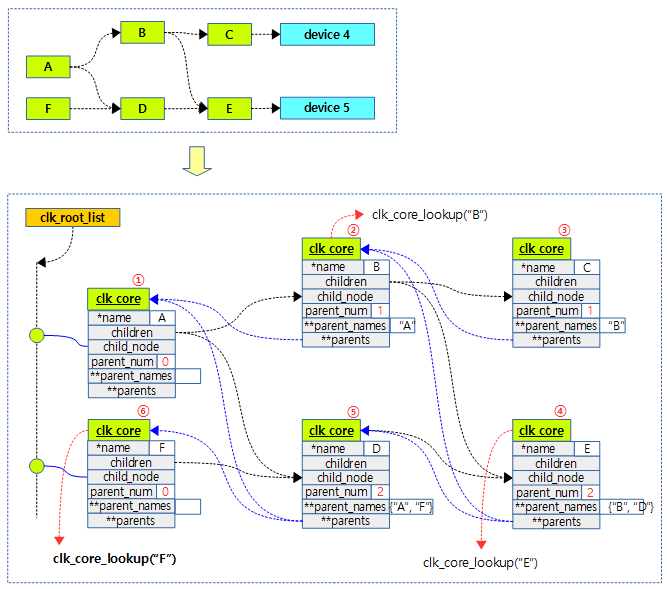

루트 클럭 리스트와 고아(orphan) 클럭 리스트에 등록된 모든 하위 클럭들을 포함하여 요청한 이름의 클럭(clk_core)을 검색한다. 검색되지 않는 경우 null을 반환한다.

- 코드 라인 10에서 clk_root_list에 등록된 루트 클럭들에 대해 루프를 돈다.

- 코드 라인 11~13에서 루트 클럭을 포함해서 하위 트리에서 요청한 이름의 클럭(clk_core)을 찾아 반환한다.

- 코드 라인 17~21에서 clk_orphan_list에 등록된 고아 클럭들에 대해 루프를 돌며 고아 클럭을 포함하여 하위 트리에서 요청한 이름의 클럭(clk_core)을 찾아 반환한다.

다음 그림은 “F”라는 이름의 클럭을 검색시 child 클럭을 검색하는 순서를 보여준다.

__clk_lookup_subtree()

drivers/clk/clk.c

static struct clk_core *__clk_lookup_subtree(const char *name,

struct clk_core *clk)

{

struct clk_core *child;

struct clk_core *ret;

if (!strcmp(clk->name, name))

return clk;

hlist_for_each_entry(child, &clk->children, child_node) {

ret = __clk_lookup_subtree(name, child);

if (ret)

return ret;

}

return NULL;

}

현재 클럭 및 그 자식 클럭에서 요청한 이름의 클럭(clk_core)을 검색한다. 검색되지 않는 경우 null을 반환한다.

- 코드 라인 7~8에서 요청한 이름의 클럭인 경우 그 클럭을 반환한다.

- 코드 라인 10에서 자식 클럭이 있는 경우 그 수 만큼 루프를 돈다.

- 코드 라인 11에서 자식 클럭과 그 이하 서브 트리를 재귀 검색한다.

- 코드 라인 12~13에서 클럭이 검색된 경우 반환한다.

clk 검색 -2- (부모 인덱스 사용)

clk_core_get_parent_by_index()

drivers/clk/clk.c

static struct clk_core *clk_core_get_parent_by_index(struct clk_core *clk,

u8 index)

{

if (!clk || index >= clk->num_parents)

return NULL;

else if (!clk->parents)

return clk_core_lookup(clk->parent_names[index]);

else if (!clk->parents[index])

return clk->parents[index] =

clk_core_lookup(clk->parent_names[index]);

else

return clk->parents[index];

}

부모 인덱스 값으로 부모 클럭을 찾아 반환한다.

- 코드 라인 4~5에서 인덱스값이 num_parents를 초과하는 경우 null을 반환한다.

- 코드 라인 7~8에서 인덱스에 해당하는 부모 클럭맵을 설정한다.

- 코드 라인 11~12에서 인덱스에 해당하는 부모 클럭을 반환한다.

clk_core_fill_parent_index()

drivers/clk/clk.c

static void clk_core_fill_parent_index(struct clk_core *core, u8 index)

{

struct clk_parent_map *entry = &core->parents[index];

struct clk_core *parent = ERR_PTR(-ENOENT);

if (entry->hw) {

parent = entry->hw->core;

/*

* We have a direct reference but it isn't registered yet?

* Orphan it and let clk_reparent() update the orphan status

* when the parent is registered.

*/

if (!parent)

parent = ERR_PTR(-EPROBE_DEFER);

} else {

parent = clk_core_get(core, index);

if (IS_ERR(parent) && PTR_ERR(parent) == -ENOENT && entry->name)

parent = clk_core_lookup(entry->name);

}

/* Only cache it if it's not an error */

if (!IS_ERR(parent))

entry->core = parent;

}

@index에 해당하는 부모 클럭맵을 설정한다.

Device Tree로 클럭 셋업

Fixed Rate 타입 Clk 디바이스 셋업

of_fixed_clk_setup()

drivers/clk/clk-fixed-rate.c

/** * of_fixed_clk_setup() - Setup function for simple fixed rate clock */

void __init of_fixed_clk_setup(struct device_node *node)

{

_of_fixed_clk_setup(node);

}

CLK_OF_DECLARE(fixed_clk, "fixed-clock", of_fixed_clk_setup);

Device Tree의 요청 클럭 노드 정보로 fixed rate 타입의 클럭을 설정한다.

_of_fixed_clk_setup()

drivers/clk/clk-fixed-rate.c

static struct clk *_of_fixed_clk_setup(struct device_node *node)

{

struct clk *clk;

const char *clk_name = node->name;

u32 rate;

u32 accuracy = 0;

if (of_property_read_u32(node, "clock-frequency", &rate))

return ERR_PTR(-EIO);

of_property_read_u32(node, "clock-accuracy", &accuracy);

of_property_read_string(node, "clock-output-names", &clk_name);

clk = clk_register_fixed_rate_with_accuracy(NULL, clk_name, NULL,

0, rate, accuracy);

if (IS_ERR(clk))

return clk;

ret = of_clk_add_provider(node, of_clk_src_simple_get, clk);

if (ret) {

clk_unregister(clk);

return ERR_PTR(ret);

}

return clk;

}

Device Tree의 요청 클럭 노드 정보로 fixed rate 타입의 클럭을 설정한다.

- 코드 라인 8~9에서 요청한 클럭 노드에서 “clock-frequency” 속성 값을 읽어 rate에 대입한다.

- 코드 라인 11에서 “clock-accuracy” 값을 읽어 accuracy에 대입한다. 속성이 없는 경우 accuracy=0 이다.

- 코드 라인 13에서 “clock-output-names” 속성 값(문자열)을 읽어 clk_name에 대입한다. 속성이 없는 경우 노드명을 사용한다.

- 코드 라인 15~18에서 읽어들인 rate, accuracy 및 clk_name으로 fixed rate 타입의 루트 클럭으로 등록한다.

- 코드 라인 20~26에서 등록이 성공된 경우 클럭 provider에 추가하고, 클럭을 반환한다.

Fixed Factor 타입 Clk 디바이스 셋업

of_fixed_factor_clk_setup()

drivers/clk/clk-fixed-factor.c

/** * of_fixed_factor_clk_setup() - Setup function for simple fixed factor clock */

void __init of_fixed_factor_clk_setup(struct device_node *node)

{

_of_fixed_factor_clk_setup(node);

}

CLK_OF_DECLARE(fixed_factor_clk, "fixed-factor-clock",

of_fixed_factor_clk_setup);

Device Tree의 요청 클럭 노드 정보로 fixed factor 타입의 클럭을 설정한다.

_of_fixed_factor_clk_setup()

drivers/clk/clk-fixed-factor.c

static struct clk_hw *_of_fixed_factor_clk_setup(struct device_node *node)

{

struct clk *clk;

const char *clk_name = node->name;

const char *parent_name;

u32 div, mult;

int ret;

if (of_property_read_u32(node, "clock-div", &div)) {

pr_err("%s Fixed factor clock <%s> must have a clock-div property\n",

__func__, node->name);

return ERR_PTR(-EIO);

}

if (of_property_read_u32(node, "clock-mult", &mult)) {

pr_err("%s Fixed factor clock <%s> must have a clock-mult property\n",

__func__, node->name);

return ERR_PTR(-EIO);

}

of_property_read_string(node, "clock-output-names", &clk_name);

if (of_match_node(set_rate_parent_matches, node))

flags |= CLK_SET_RATE_PARENT;

hw = __clk_hw_register_fixed_factor(NULL, node, clk_name, NULL, 0,

flags, mult, div);

if (IS_ERR(hw)) {

/*

* Clear OF_POPULATED flag so that clock registration can be

* attempted again from probe function.

*/

of_node_clear_flag(node, OF_POPULATED);

return ERR_CAST(hw);

}

ret = of_clk_add_hw_provider(node, of_clk_hw_simple_get, hw);

if (ret) {

clk_hw_unregister_fixed_factor(hw);

return ERR_PTR(ret);

}

return hw;

}

Device Tree의 요청 클럭 노드 정보로 fixed factor 타입의 클럭을 설정한다.

- 코드 라인 9~13에서 요청한 클럭 노드에서 “clock-div” 속성 값을 읽어 div에 대입한다.

- 코드 라인 15~19에서 “clock-mult” 값을 읽어 multi에 대입한다.

- 코드 라인 21에서 “clock-output-names” 속성 값(문자열)을 읽어 clk_name에 대입한다. 속성이 없는 경우 노드명을 사용한다.

- 코드 라인 23~24에서 디바이스 노드가 set_rate_parent_matches[]에 적합한 드라이버인 경우 CLK_SET_RATE_PARENT 플래그를 설정한다.

- 코드 라인 26~35에서 읽어들인 div, multi, parent_name 및 clk_name으로 fixed factor 타입의 클럭으로 등록한다.

- 코드 라인 37~43에서 등록이 성공된 경우 클럭 provider에 추가하고 clk_hw를 반환한다.

다음 그림은 rpi2의 Device Tree Script (커널 v4.10 기준)에서 각 clock에 대한 연관도를 보여준다.

- /soc/cprman은 플랫폼 클럭 장치로 7개의 클럭을 제공하고 4개의 클럭 입력을 받는다.

- /soc/aux 디바이스는 3 개의 gate clock 장치이다. (0번은 aux_uart용으로 spi1 및 spi2 장치와 인터럽트가 공유된다.)

- /soc/dsi1 디바이스는 GPU용 DSI 장치이다.

타입별 클럭 등록 함수

9개 타입의 클럭에 대해 multiplier 타입을 제외한 등록 함수들이 API로 제공된다. 그리고 fixed rate 및 fixed factor 타입의 경우 디바이스 트리를 사용한 API도 제공된다. 소스 분석은 fixed rate 타입과 fixed factor 타입으로 제한하였다.

- multiplier 타입의 경우는 아직 composite 타입에 연동하여 사용되므로 등록 함수는 제외된다.

다음 그림과 같이 클럭은 3가지 형태로 구분할 수 있으며 총 9개의 타입을 가지고 있으며 각각의 등록 함수를 보여준다.

common 클럭 타입별 ops

composite 타입을 제외한 ops를 알아본다. composite 타입의 경우 별도의 ops를 사용하지 않고, 다른 클럭 타입들 중 rate, mux 및 gate 클럭의 ops를 두 개 이상 지정하여 복합 구성할 수 있다.

clk_fixed_rate_ops

/drivers/clk/clk-fixed-rate.c

const struct clk_ops clk_fixed_rate_ops = {

.recalc_rate = clk_fixed_rate_recalc_rate,

.recalc_accuracy = clk_fixed_rate_recalc_accuracy,

};

EXPORT_SYMBOL_GPL(clk_fixed_rate_ops);

clk_fixed_factor_ops

/drivers/clk/clk-fixed-factor.c

const struct clk_ops clk_fixed_factor_ops = {

.round_rate = clk_factor_round_rate,

.set_rate = clk_factor_set_rate,

.recalc_rate = clk_factor_recalc_rate,

};

EXPORT_SYMBOL_GPL(clk_fixed_factor_ops);

clk_divider_ops

/drivers/clk/clk-divider.c

const struct clk_ops clk_divider_ops = {

.recalc_rate = clk_divider_recalc_rate,

.round_rate = clk_divider_round_rate,

.set_rate = clk_divider_set_rate,

};

EXPORT_SYMBOL_GPL(clk_divider_ops);

clk_divider_ro_ops

/drivers/clk/clk-divider.c

const struct clk_ops clk_divider_ro_ops = {

.recalc_rate = clk_divider_recalc_rate,

.round_rate = clk_divider_round_rate,

};

EXPORT_SYMBOL_GPL(clk_divider_ro_ops);

- CLK_DIVIDER_READ_ONLY 플래그를 사용하는 경우 사용되는 ops이다.

clk_fractional_divider_ops

/drivers/clk/

const struct clk_ops clk_fractional_divider_ops = {

.recalc_rate = clk_fd_recalc_rate,

.round_rate = clk_fd_round_rate,

.set_rate = clk_fd_set_rate,

};

EXPORT_SYMBOL_GPL(clk_fractional_divider_ops);

clk_multiplier_ops

/drivers/clk/clk-fractional-divider.c

const struct clk_ops clk_multiplier_ops = {

.recalc_rate = clk_multiplier_recalc_rate,

.round_rate = clk_multiplier_round_rate,

.set_rate = clk_multiplier_set_rate,

};

EXPORT_SYMBOL_GPL(clk_multiplier_ops);

clk_mux_ops

/drivers/clk/clk-mux.c

const struct clk_ops clk_mux_ops = {

.get_parent = clk_mux_get_parent,

.set_parent = clk_mux_set_parent,

.determine_rate = clk_mux_determine_rate,

};

EXPORT_SYMBOL_GPL(clk_mux_ops);

clk_mux_ro_ops

/drivers/clk/clk-mux.c

const struct clk_ops clk_mux_ro_ops = {

.get_parent = clk_mux_get_parent,

};

EXPORT_SYMBOL_GPL(clk_mux_ro_ops);

- CLK_MUX_READ_ONLY 플래그를 사용하는 경우 사용되는 ops이다.

clk_gpio_gate_ops

/drivers/clk/clk-gpio.c

const struct clk_ops clk_gpio_gate_ops = {

.enable = clk_gpio_gate_enable,

.disable = clk_gpio_gate_disable,

.is_enabled = clk_gpio_gate_is_enabled,

};

EXPORT_SYMBOL_GPL(clk_gpio_gate_ops);

clk_gate_ops

/drivers/clk/clk-gate.c

const struct clk_ops clk_gate_ops = {

.enable = clk_gate_enable,

.disable = clk_gate_disable,

.is_enabled = clk_gate_is_enabled,

};

EXPORT_SYMBOL_GPL(clk_gate_ops);

Fixed Rate 타입 Clk 등록

clk_register_fixed_rate()

drivers/clk/clk-fixed-rate.c

struct clk *clk_register_fixed_rate(struct device *dev, const char *name,

const char *parent_name, unsigned long flags,

unsigned long fixed_rate)

{

return clk_register_fixed_rate_with_accuracy(dev, name, parent_name,

flags, fixed_rate, 0);

}

EXPORT_SYMBOL_GPL(clk_register_fixed_rate);

클럭 디바이스, @name, @parent_name, @flags, @fixed_rate 정보를 인수로 accuracy가 0인 fixed rate 타입의 클럭을 등록한다.

clk_register_fixed_rate_with_accuracy()

drivers/clk/clk-fixed-rate.c

struct clk *clk_register_fixed_rate_with_accuracy(struct device *dev,

const char *name, const char *parent_name, unsigned long flags,

unsigned long fixed_rate, unsigned long fixed_accuracy)

{

struct clk_hw *hw;

hw = clk_hw_register_fixed_rate_with_accuracy(dev, name, parent_name,

flags, fixed_rate, fixed_accuracy);

if (IS_ERR(hw))

return ERR_CAST(hw);

return hw->clk;

}

EXPORT_SYMBOL_GPL(clk_register_fixed_rate_with_accuracy);

클럭 디바이스, @name, @parent_name, @flags, @fixed_rate, @fixed_accuracy 정보를 인수로 받아 fixed rate 타입의 클럭을 등록한다.

clk_hw_register_fixed_rate()

drivers/clk/clk-fixed-rate.c

/** * clk_hw_register_fixed_rate - register fixed-rate clock with the clock * framework * @dev: device that is registering this clock * @name: name of this clock * @parent_name: name of clock's parent * @flags: framework-specific flags * @fixed_rate: non-adjustable clock rate */

struct clk_hw *clk_hw_register_fixed_rate(struct device *dev, const char *name,

const char *parent_name, unsigned long flags,

unsigned long fixed_rate)

{

return clk_hw_register_fixed_rate_with_accuracy(dev, name, parent_name,

flags, fixed_rate, 0);

}

EXPORT_SYMBOL_GPL(clk_hw_register_fixed_rate);

클럭 디바이스, @name, @parent_name, @flags, @fixed_rate 정보를 인수로 accuracy가 0인 fixed rate 타입의 클럭을 등록한다.

clk_hw_register_fixed_rate_with_accuracy()

drivers/clk/clk-fixed-rate.c

/** * clk_hw_register_fixed_rate_with_accuracy - register fixed-rate clock with * the clock framework * @dev: device that is registering this clock * @name: name of this clock * @parent_name: name of clock's parent * @flags: framework-specific flags * @fixed_rate: non-adjustable clock rate * @fixed_accuracy: non-adjustable clock rate */

struct clk_hw *clk_hw_register_fixed_rate_with_accuracy(struct device *dev,

const char *name, const char *parent_name, unsigned long flags,

unsigned long fixed_rate, unsigned long fixed_accuracy)

{

struct clk_fixed_rate *fixed;

struct clk_hw *hw;

struct clk_init_data init;

int ret;

/* allocate fixed-rate clock */

fixed = kzalloc(sizeof(*fixed), GFP_KERNEL);

if (!fixed)

return ERR_PTR(-ENOMEM);

init.name = name;

init.ops = &clk_fixed_rate_ops;

init.flags = flags;

init.parent_names = (parent_name ? &parent_name: NULL);

init.num_parents = (parent_name ? 1 : 0);

/* struct clk_fixed_rate assignments */

fixed->fixed_rate = fixed_rate;

fixed->fixed_accuracy = fixed_accuracy;

fixed->hw.init = &init;

/* register the clock */

hw = &fixed->hw;

ret = clk_hw_register(dev, hw);

if (ret) {

kfree(fixed);

hw = ERR_PTR(ret);

}

return hw;

}

EXPORT_SYMBOL_GPL(clk_hw_register_fixed_rate_with_accuracy);

클럭 디바이스, @name, @parent_name, @flags, @fixed_rate, @fixed_accuracy 정보를 인수로 받아 fixed rate 타입의 클럭을 등록한다.

- 코드 라인 11~19에서 clk_fixed_rate 구조체를 할당받아 fixed rate 클럭에대한 기본 정보를 구성한다.

- 코드 라인 22~24에서 @fixed_rate, @fixed_accuracy 등을 추가하여 구성한다.

- 코드 라인 27~34에서 클럭을 등록한 후 clk_hw를 반환한다.

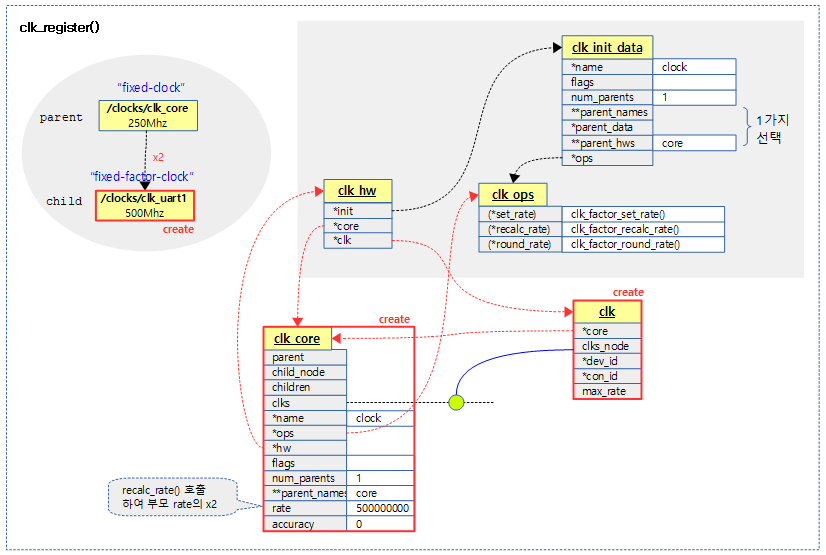

다음 그림은 fixed rate 타입의 클럭을 등록하는 모습을 보여준다.

Fixed Factor 타입 Clk 등록

clk_register_fixed_factor()

drivers/clk/clk-fixed-factor.c

struct clk *clk_register_fixed_factor(struct device *dev, const char *name,

const char *parent_name, unsigned long flags,

unsigned int mult, unsigned int div)

{

struct clk_hw *hw;

hw = clk_hw_register_fixed_factor(dev, name, parent_name, flags, mult,

div);

if (IS_ERR(hw))

return ERR_CAST(hw);

return hw->clk;

}

EXPORT_SYMBOL_GPL(clk_register_fixed_factor);

클럭 디바이스, @name, @parent_name, @flags, @multi, @div 정보를 인수로 받아 fixed factor 타입의 클럭을 등록한다.

clk_hw_register_fixed_factor()

drivers/clk/clk-fixed-factor.c

struct clk_hw *clk_hw_register_fixed_factor(struct device *dev,

const char *name, const char *parent_name, unsigned long flags,

unsigned int mult, unsigned int div)

{

return __clk_hw_register_fixed_factor(dev, NULL, name, parent_name, -1,

flags, mult, div);

}

EXPORT_SYMBOL_GPL(clk_hw_register_fixed_factor);

클럭 디바이스, @name, @parent_name, @flags, @multi, @div 정보를 인수로 받아 fixed factor 타입의 클럭을 등록한다.

__clk_hw_register_fixed_factor()

drivers/clk/clk-fixed-factor.c

static struct clk_hw *

__clk_hw_register_fixed_factor(struct device *dev, struct device_node *np,

const char *name, const char *parent_name, int index,

unsigned long flags, unsigned int mult, unsigned int div)

{

struct clk_fixed_factor *fix;

struct clk_init_data init = { };

struct clk_parent_data pdata = { .index = index };

struct clk_hw *hw;

int ret;

fix = kmalloc(sizeof(*fix), GFP_KERNEL);

if (!fix)

return ERR_PTR(-ENOMEM);

/* struct clk_fixed_factor assignments */

fix->mult = mult;

fix->div = div;

fix->hw.init = &init;

init.name = name;

init.ops = &clk_fixed_factor_ops;

init.flags = flags;

if (parent_name)

init.parent_names = &parent_name;

else

init.parent_data = &pdata;

init.num_parents = 1;

hw = &fix->hw;

if (dev)

ret = clk_hw_register(dev, hw);

else

ret = of_clk_hw_register(np, hw);

if (ret) {

kfree(fix);

hw = ERR_PTR(ret);

}

return hw;

}

클럭 디바이스, @name, @parent_name, @flags, multi, @div 정보를 인수로 받아 fixed factor 타입의 클럭을 등록한다.

- 코드 라인 12~14에서 clk_fixed_facotr 구조체를 할당받고 multi 값과 div 값 등을 구성한다.

- 코드 라인 17~28에서 할당 받은 구조체를 fixed factor 타입으로 구성한다.

- 코드 라인 30~40에서 클럭을 등록한다

Clk 등록

clk_register()

drivers/clk/clk.c

/** * clk_register - allocate a new clock, register it and return an opaque cookie * @dev: device that is registering this clock * @hw: link to hardware-specific clock data * * clk_register is the *deprecated* interface for populating the clock tree with * new clock nodes. Use clk_hw_register() instead. * * Returns: a pointer to the newly allocated struct clk which * cannot be dereferenced by driver code but may be used in conjunction with the * rest of the clock API. In the event of an error clk_register will return an * error code; drivers must test for an error code after calling clk_register. */

struct clk *clk_register(struct device *dev, struct clk_hw *hw)

{

return __clk_register(dev, dev_of_node(dev), hw);

}

EXPORT_SYMBOL_GPL(clk_register);

요청한 클럭 디바이스를 할당하여 등록한다.

- 디바이스와 @hw 정보로 clk_core와 clk를 구성하여 등록하고 최상위 노드인 경우 초기화한다.

static struct clk *

__clk_register(struct device *dev, struct device_node *np, struct clk_hw *hw)

{

int ret;

struct clk_core *core;

const struct clk_init_data *init = hw->init;

/*

* The init data is not supposed to be used outside of registration path.

* Set it to NULL so that provider drivers can't use it either and so that

* we catch use of hw->init early on in the core.

*/

hw->init = NULL;

core = kzalloc(sizeof(*core), GFP_KERNEL);

if (!core) {

ret = -ENOMEM;

goto fail_out;

}

core->name = kstrdup_const(init->name, GFP_KERNEL);

if (!core->name) {

ret = -ENOMEM;

goto fail_name;

}

if (WARN_ON(!init->ops)) {

ret = -EINVAL;

goto fail_ops;

}

core->ops = init->ops;

if (dev && pm_runtime_enabled(dev))

core->rpm_enabled = true;

core->dev = dev;

core->of_node = np;

if (dev && dev->driver)

core->owner = dev->driver->owner;

core->hw = hw;

core->flags = init->flags;

core->num_parents = init->num_parents;

core->min_rate = 0;

core->max_rate = ULONG_MAX;

hw->core = core;

ret = clk_core_populate_parent_map(core, init);

if (ret)

goto fail_parents;

INIT_HLIST_HEAD(&core->clks);

/*

* Don't call clk_hw_create_clk() here because that would pin the

* provider module to itself and prevent it from ever being removed.

*/

hw->clk = alloc_clk(core, NULL, NULL);

if (IS_ERR(hw->clk)) {

ret = PTR_ERR(hw->clk);

goto fail_create_clk;

}

clk_core_link_consumer(hw->core, hw->clk);

ret = __clk_core_init(core);

if (!ret)

return hw->clk;

clk_prepare_lock();

clk_core_unlink_consumer(hw->clk);

clk_prepare_unlock();

free_clk(hw->clk);

hw->clk = NULL;

fail_create_clk:

clk_core_free_parent_map(core);

fail_parents:

fail_ops:

kfree_const(core->name);

fail_name:

kfree(core);

fail_out:

return ERR_PTR(ret);

}

요청한 클럭 디바이스를 할당하여 등록한다.

- 코드 라인 6에서 클럭 init 데이터를 클럭 core에 복사할 목적으로 init 포인터에 대입한다.

- 코드 라인 15~19에서 clk_core 구조체를 할당받아 core에 대입한다.

- 코드 라인 21~25에서 core->name에 hw->init->name의 복사본 문자열을 대입한다.

- kstrdup_const()

- 문자열이 rodata(읽기 전용 커널 데이터) 섹션에 위치한 경우 복제하지 않고 const 타입으로 그냥 사용한다.

- kstrdup_const()

- 코드 라인 27~31에서 클럭 init 데이터로 넘겨 받은 클럭의 ops를 지정한다.

- 코드 라인 33~44에서 클럭 init 데이터를 사용하여 clk_core 구조체를 구성한다.

- 코드 라인 46~48에서 부모 클럭 맵을 준비한다.

- 코드 라인 50에서 core->clks 리스트를 초기화한다.

- 코드 라인 56~60에서 clk를 할당받아 구성한다.

- 코드 라인 62에서 클럭 core를 클럭 리스트에 추가한다.

- 코드 라인 64~66에서 클럭 core를 초기화하고, 성공한 경우 클럭을 반환한다.

- 코드 라인 68~83에서 클럭 core 등록이 실패한 경우 생성했던 모든 객체들을 free 시키고 에러를 반환한다.

다음 그림은 부모 노드를 가진 클럭을 등록하는 모습을 보여준다.

다음 그림은 등록된 클럭의 부모 관계를 보여준다. 클럭을 사용하는 관점에서 Consumer용 클럭도 같이 표현하였다.

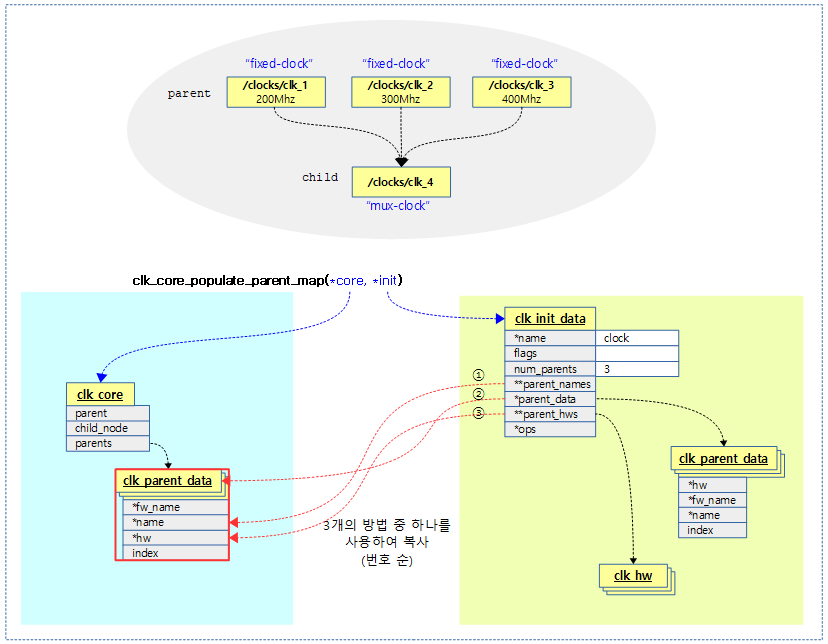

clk_core_populate_parent_map()

drivers/clk/clk.c

static int clk_core_populate_parent_map(struct clk_core *core,

const struct clk_init_data *init)

{

u8 num_parents = init->num_parents;

const char * const *parent_names = init->parent_names;

const struct clk_hw **parent_hws = init->parent_hws;

const struct clk_parent_data *parent_data = init->parent_data;

int i, ret = 0;

struct clk_parent_map *parents, *parent;

if (!num_parents)

return 0;

/*

* Avoid unnecessary string look-ups of clk_core's possible parents by

* having a cache of names/clk_hw pointers to clk_core pointers.

*/

parents = kcalloc(num_parents, sizeof(*parents), GFP_KERNEL);

core->parents = parents;

if (!parents)

return -ENOMEM;

/* Copy everything over because it might be __initdata */

for (i = 0, parent = parents; i < num_parents; i++, parent++) {

parent->index = -1;

if (parent_names) {

/* throw a WARN if any entries are NULL */

WARN(!parent_names[i],

"%s: invalid NULL in %s's .parent_names\n",

__func__, core->name);

ret = clk_cpy_name(&parent->name, parent_names[i],

true);

} else if (parent_data) {

parent->hw = parent_data[i].hw;

parent->index = parent_data[i].index;

ret = clk_cpy_name(&parent->fw_name,

parent_data[i].fw_name, false);

if (!ret)

ret = clk_cpy_name(&parent->name,

parent_data[i].name,

false);

} else if (parent_hws) {

parent->hw = parent_hws[i];

} else {

ret = -EINVAL;

WARN(1, "Must specify parents if num_parents > 0\n");

}

if (ret) {

do {

kfree_const(parents[i].name);

kfree_const(parents[i].fw_name);

} while (--i >= 0);

kfree(parents);

return ret;

}

}

return 0;

}

요청한 클럭의 부모들을 연결하는 부모 맵을 구성한다. @init에서 넘겨준 parent_names, parent_data 또는 parent_hws 라는 세 가지 정보들 중 하나로 부모 정보를 구성한다.

- 코드 라인 11~12에서 부모 클럭이 없는 경우 성공 값으로 0을 반환한다.

- 코드 라인 18~21에서 부모 수 만큼 clk_parent_data 구조체를 할당받는다.

- 코드 라인 24~47에서 @init 정보에 포함된 부모 클럭 정보를 가져와서 구성한다. 다음 순서 중 하나를 선택하여 구성한다.

- init->parent_names[] 정보가 제공된 경우 이 이름 정보만으로 구성한다.

- init->parent_data[] 정보가 제공된 경우 이 구성 정보를 그대로 복사하여 구성한다.

- init->parent_hws[] 정보가 제공된 경우 이 hws 정보를 그대로 이용한다.

- 코드 라인 49~58에서 부모 정보가 제대로 제공되지 않은 경우 할당 했었던 정보를 할당 해제 후 에러를 반환한다.

- 코드 라인 60에서 에러 없이 모든 부모 정보를 구성한 경우 성공 값으로 0을 반환한다.

다음 그림은 해당 클럭의 부모들 연결하는 부모 맵을 구성하는 과정을 보여준다.

alloc_clk()

drivers/clk/clk.c

/** * alloc_clk - Allocate a clk consumer, but leave it unlinked to the clk_core * @core: clk to allocate a consumer for * @dev_id: string describing device name * @con_id: connection ID string on device * * Returns: clk consumer left unlinked from the consumer list */

static struct clk *alloc_clk(struct clk_core *core, const char *dev_id,

const char *con_id)

{

struct clk *clk;

clk = kzalloc(sizeof(*clk), GFP_KERNEL);

if (!clk)

return ERR_PTR(-ENOMEM);

clk->core = core;

clk->dev_id = dev_id;

clk->con_id = kstrdup_const(con_id, GFP_KERNEL);

clk->max_rate = ULONG_MAX;

return clk;

}

클럭을 할당하고 구성한 후 반환한다.

__clk_core_init()

drivers/clk/clk.c -1/3-

/** * __clk_core_init - initialize the data structures in a struct clk_core * @core: clk_core being initialized * * Initializes the lists in struct clk_core, queries the hardware for the * parent and rate and sets them both. */

static int __clk_core_init(struct clk_core *core)

{

int ret;

struct clk_core *orphan;

struct hlist_node *tmp2;

unsigned long rate;

if (!core)

return -EINVAL;

clk_prepare_lock();

ret = clk_pm_runtime_get(core);

if (ret)

goto unlock;

/* check to see if a clock with this name is already registered */

if (clk_core_lookup(core->name)) {

pr_debug("%s: clk %s already initialized\n",

__func__, core->name);

ret = -EEXIST;

goto out;

}

/* check that clk_ops are sane. See Documentation/driver-api/clk.rst */

if (core->ops->set_rate &&

!((core->ops->round_rate || core->ops->determine_rate) &&

core->ops->recalc_rate)) {

pr_err("%s: %s must implement .round_rate or .determine_rate in addition to .recalc__

rate\n",

__func__, core->name);

ret = -EINVAL;

goto out;

}

if (core->ops->set_parent && !core->ops->get_parent) {

pr_err("%s: %s must implement .get_parent & .set_parent\n",

__func__, core->name);

ret = -EINVAL;

goto out;

}

if (core->num_parents > 1 && !core->ops->get_parent) {

pr_err("%s: %s must implement .get_parent as it has multi parents\n",

__func__, core->name);

ret = -EINVAL;

goto out;

}

if (core->ops->set_rate_and_parent &&

!(core->ops->set_parent && core->ops->set_rate)) {

pr_err("%s: %s must implement .set_parent & .set_rate\n",

__func__, core->name);

ret = -EINVAL;

goto out;

}

core->parent = __clk_init_parent(core);

클럭을 초기화한다. 이 때 부모 클럭 관계와 rate, accuracy 등을 설정한다.

- 코드 라인 18~23에서 이름으로 클럭을 검색하여 이미 존재하는 경우 -EEXIST 에러를 반환한다.

- 코드 라인 26~34에서 rate가 고정된 fixed rate 타입을 제외하고 나머지 rate를 설정할 수 있는 클럭들의 경우 (*set_rate) 후크 함수가 주어진다. 이 때 (*recalc_rate)가 준비되어야 하고, (*round_rate) 또는 (*determine_rate) 둘 중 하나의 후크 함수가 필요하므로 이를 체크한다.

- fixed-factor, divider, multiplier, fractional-divider 클럭 타입등이 해당된다.

- 코드 라인 36~41에서 mux 클럭의 경우 (*set_parent) 후크가 주어진다. 이 때 (*get_parent)도 필요하므로 체크한다.

- 코드 라인 43~48에서 2개 이상의 부모를 가진 mux 클럭의 경우 (*get_parent) 후크 함수가 필요한다.

- 코드 라인 50~56에서 부모의 클럭 rate를 변경할 수 있는 (*set_rate_and_parent) 후크 함수를 가진 클럭인 경우 (*set_parent)와 (*set_rate) 후크 함수를 필요로 한다.

- 이 기능은 common 클럭 타입에는 없고, 일부 custom 클럭에서 제공되고 있다.

- 코드 라인 58에서 최초 연결될 부모 클럭맵을 구성하고 부모 클럭을 알아온다.

drivers/clk/clk.c -2/3-

. /*

* Populate core->parent if parent has already been clk_core_init'd. If

* parent has not yet been clk_core_init'd then place clk in the orphan

* list. If clk doesn't have any parents then place it in the root

* clk list.

*

* Every time a new clk is clk_init'd then we walk the list of orphan

* clocks and re-parent any that are children of the clock currently

* being clk_init'd.

*/

if (core->parent) {

hlist_add_head(&core->child_node,

&core->parent->children);

core->orphan = core->parent->orphan;

} else if (!core->num_parents) {

hlist_add_head(&core->child_node, &clk_root_list);

core->orphan = false;

} else {

hlist_add_head(&core->child_node, &clk_orphan_list);

core->orphan = true;

}

/*

* optional platform-specific magic

*

* The .init callback is not used by any of the basic clock types, but

* exists for weird hardware that must perform initialization magic.

* Please consider other ways of solving initialization problems before

* using this callback, as its use is discouraged.

*/

if (core->ops->init)

core->ops->init(core->hw);

/*

* Set clk's accuracy. The preferred method is to use

* .recalc_accuracy. For simple clocks and lazy developers the default

* fallback is to use the parent's accuracy. If a clock doesn't have a

* parent (or is orphaned) then accuracy is set to zero (perfect

* clock).

*/

if (core->ops->recalc_accuracy)

core->accuracy = core->ops->recalc_accuracy(core->hw,

__clk_get_accuracy(core->parent));

else if (core->parent)

core->accuracy = core->parent->accuracy;

else

core->accuracy = 0;

/*

* Set clk's phase.

* Since a phase is by definition relative to its parent, just

* query the current clock phase, or just assume it's in phase.

*/

if (core->ops->get_phase)

core->phase = core->ops->get_phase(core->hw);

else

core->phase = 0;

/*

* Set clk's duty cycle.

*/

clk_core_update_duty_cycle_nolock(core);

/*

* Set clk's rate. The preferred method is to use .recalc_rate. For

* simple clocks and lazy developers the default fallback is to use the

* parent's rate. If a clock doesn't have a parent (or is orphaned)

* then rate is set to zero.

*/

if (core->ops->recalc_rate)

rate = core->ops->recalc_rate(core->hw,

clk_core_get_rate_nolock(core->parent));

else if (core->parent)

rate = core->parent->rate;

else

rate = 0;

core->rate = core->req_rate = rate;

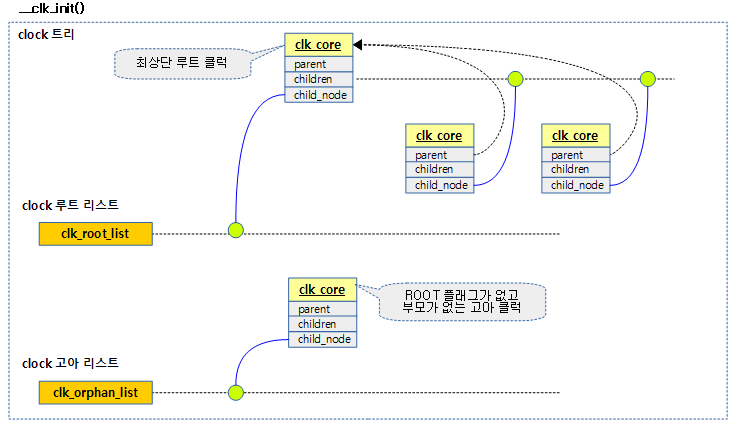

- 코드 라인 11~21에서 클럭의 하이라키를 구성한다.

- 부모 클럭이 지정된 경우 부모 클럭의 children 리스트에 등록한다.

- 루트 클럭인 경우 clk_root_list에 등록한다.

- 고아(orphan) 클럭인 경우 clk_orphan_list에 등록한다.

- clk_root_list에 root 클럭만 추가되듯이,

- clk_orphan_list에는 고아 클럭들 중 상위 부모만 추가된다.

- 예) (A 고아) — B – C

- A만 clk_orphan_list에 추가된다.

- 예) (A 고아) — B – C

- 모든 clock core들은 반드시 다음 3가지 리스트 중 하나에 연결된다.

- clk_root_list

- clk_orphan_list

- 부모의 children 리스트

- 코드 라인 31~32에서 클럭 초기화를 위해 아키텍처가 지원하는 별도의 (*init) 후크 함수를 수행한다.

- common 클럭 타입에는 없고, 일부 custom 클럭에서 제공되고 있다.

- 코드 라인 41~47에서 클럭의 정확도(accuracy)를 설정한다.

- fixed rate 타입의 클럭인 경우 (*recalc_accuracy) 후크 함수를 수행하여 클럭의 정확도(accuracy)를 설정한다.

- 그렇지 않은 경우 부모 클럭이 있으면 부모 클럭의 accuracy 값을 사용하고, 없으면 0을 설정한다.

- 코드 라인 54~57에서 custom 클럭들 중 클럭의 위상(phase)을 지정하는 클럭들이 있다. 이러한 클럭의 위상(phase)을 설정한다.

- (*get_phase) 후크 함수를 수행하여 phase 값을 알아오고, 해당 후크 함수가 없으면 0으로 설정한다.

- 코드 라인 62에서 클럭의 duty cycle을 지정한다.

- duty 사이클은 on에 해당하는 시간 / 1 주기 시간에 대한 백분율이다.

- 참고: Duty Cycle | Wikipedia

- 코드 라인 70~77에서 클럭의 rate를 설정한다.

- rate 타입의 클럭인 경우 (*recalc_rate) 후크 함수를 지원하므로 이를 통해 rate 값을 구해온다.

- rate 타입의 클럭이 아닌 경우 부모의 rate를 사용하거나 부모가 없으면 0으로 설정한다.

drivers/clk/clk.c -3/3-

/*

* Enable CLK_IS_CRITICAL clocks so newly added critical clocks

* don't get accidentally disabled when walking the orphan tree and

* reparenting clocks

*/

if (core->flags & CLK_IS_CRITICAL) {

unsigned long flags;

clk_core_prepare(core);

flags = clk_enable_lock();

clk_core_enable(core);

clk_enable_unlock(flags);

}

/*

* walk the list of orphan clocks and reparent any that newly finds a

* parent.

*/

hlist_for_each_entry_safe(orphan, tmp2, &clk_orphan_list, child_node) {

struct clk_core *parent = __clk_init_parent(orphan);

/*

* We need to use __clk_set_parent_before() and _after() to

* to properly migrate any prepare/enable count of the orphan

* clock. This is important for CLK_IS_CRITICAL clocks, which

* are enabled during init but might not have a parent yet.

*/

if (parent) {

/* update the clk tree topology */

__clk_set_parent_before(orphan, parent);

__clk_set_parent_after(orphan, parent, NULL);

__clk_recalc_accuracies(orphan);

__clk_recalc_rates(orphan, 0);

}

}

kref_init(&core->ref);

out:

clk_pm_runtime_put(core);

unlock:

clk_prepare_unlock();

if (!ret)

clk_debug_register(core);

return ret;

}

- 코드 라인 6~14에서 CLK_IS_CRITICAL 플래그를 사용한 경우 일시적으로 고아(orphan) 클럭이었다가 부모 클럭이 활성화되지 않은 상태에 놓여있어도 클럭이 항상 동작하게 한다.

- 참고: clk: migrate the count of orphaned clocks at init (2018, v4.16-rc7)

- 코드 라인 20~36에서 고아 클럭 리스트인 clk_orphan_list에 등록된 클럭들을 순회하며 부모 클럭이 발견되면 이에 대한 accuracy 및 rate 설정을 다시 한다.

다음 그림은 clock 루트 리스트에 포함되는 클럭과 clock 고아 리스트에 포함되는 클럭의 속성 차이를 보여준다.

__clk_init_parent()

drivers/clk/clk.c

static struct clk_core *__clk_init_parent(struct clk_core *core)

{

u8 index = 0;

if (core->num_parents > 1 && core->ops->get_parent)

index = core->ops->get_parent(core->hw);

return clk_core_get_parent_by_index(core, index);

}

부모 클럭을 알아와서 연결한다.

클럭 Provider

다음과 같이 클럭 provider를 추가하는 두 개의 API가 지원된다.

- of_clk_add_provider()

- of_clk_add_hw_provider()

- 참고: clk: Add clk_hw OF clk providers (2016, v4.7-rc1)

클럭 provider 추가 -1-

of_clk_add_provider()

drivers/clk/clk.c

/** * of_clk_add_provider() - Register a clock provider for a node * @np: Device node pointer associated with clock provider * @clk_src_get: callback for decoding clock * @data: context pointer for @clk_src_get callback. * * This function is *deprecated*. Use of_clk_add_hw_provider() instead. */

int of_clk_add_provider(struct device_node *np,

struct clk *(*clk_src_get)(struct of_phandle_args *clkspec,

void *data),

void *data)

{

struct of_clk_provider *cp;

int ret;

cp = kzalloc(sizeof(*cp), GFP_KERNEL);

if (!cp)

return -ENOMEM;

cp->node = of_node_get(np);

cp->data = data;

cp->get = clk_src_get;

mutex_lock(&of_clk_mutex);

list_add(&cp->link, &of_clk_providers);

mutex_unlock(&of_clk_mutex);

pr_debug("Added clock from %pOF\n", np);

ret = of_clk_set_defaults(np, true);

if (ret < 0)

of_clk_del_provider(np);

return ret;

}

EXPORT_SYMBOL_GPL(of_clk_add_provider);

디바이스 노드의 클럭 provder를 추가한다. 추가 시 clk를 반환하는 함수를 지정한다. 성공하면 0을 반환한다.

- 코드 라인 9~15에서 of_clk_provider 구조체를 할당받아 구성한다.

- 코드 라인 17~20에서 of_clk_providers에 추가하고 디버그 메시지를 출력한다.

- 코드 라인 22~24에서 default 부모 클럭과 rate를 설정한다. 만일 실패하는 경우 provider 리스트에서 제거한다.

- 코드 라인 26에서 클럭 설정 결과를 반환한다. 성공 시 0을 반환한다.

클럭 공급자 추가 -2-

of_clk_add_hw_provider()

drivers/clk/clk.c

/** * of_clk_add_hw_provider() - Register a clock provider for a node * @np: Device node pointer associated with clock provider * @get: callback for decoding clk_hw * @data: context pointer for @get callback. */

int of_clk_add_hw_provider(struct device_node *np,

struct clk_hw *(*get)(struct of_phandle_args *clkspec,

void *data),

void *data)

{

struct of_clk_provider *cp;

int ret;

cp = kzalloc(sizeof(*cp), GFP_KERNEL);

if (!cp)

return -ENOMEM;

cp->node = of_node_get(np);

cp->data = data;

cp->get_hw = get;

mutex_lock(&of_clk_mutex);

list_add(&cp->link, &of_clk_providers);

mutex_unlock(&of_clk_mutex);

pr_debug("Added clk_hw provider from %pOF\n", np);

ret = of_clk_set_defaults(np, true);

if (ret < 0)

of_clk_del_provider(np);

return ret;

}

EXPORT_SYMBOL_GPL(of_clk_add_hw_provider);

디바이스 노드의 클럭 provider를 추가한다. 추가 시 clk_hw를 반환하는 함수를 지정한다. 성공하면 0을 반환한다.

- 코드 라인 9~15에서 of_clk_provider 구조체를 할당받아 구성한다.

- 코드 라인 17~20에서 of_clk_providers에 추가하고 디버그 메시지를 출력한다.

- 코드 라인 22~24에서 default 부모 클럭과 rate를 설정한다. 만일 실패하는 경우 provider 리스트에서 제거한다.

- 코드 라인 26에서 클럭 설정 결과를 반환한다. 성공 시 0을 반환한다.

Provider에 등록된 클럭 사용

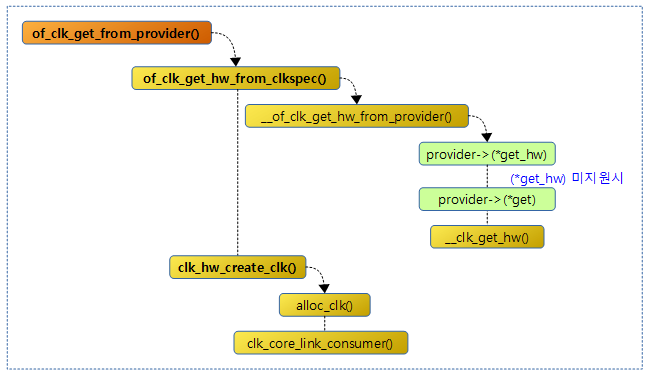

다음 그림은 provider에 등록된 클럭을 사용하는 함수 이후의 호출 과정을 보여준다.

of_clk_get_from_provider()

drivers/clk/clk.c

/** * of_clk_get_from_provider() - Lookup a clock from a clock provider * @clkspec: pointer to a clock specifier data structure * * This function looks up a struct clk from the registered list of clock * providers, an input is a clock specifier data structure as returned * from the of_parse_phandle_with_args() function call. */

struct clk *of_clk_get_from_provider(struct of_phandle_args *clkspec)

{

struct clk_hw *hw = of_clk_get_hw_from_clkspec(clkspec);

return clk_hw_create_clk(NULL, hw, NULL, __func__);

}

EXPORT_SYMBOL_GPL(of_clk_get_from_provider);

클럭 providers 리스트에서 of_phandle_args 값으로 클럭을 검색하여 반환한다.

of_clk_get_hw_from_clkspec()

drivers/clk/clk.c

static struct clk_hw *

of_clk_get_hw_from_clkspec(struct of_phandle_args *clkspec)

{

struct of_clk_provider *provider;

struct clk_hw *hw = ERR_PTR(-EPROBE_DEFER);

if (!clkspec)

return ERR_PTR(-EINVAL);

mutex_lock(&of_clk_mutex);

list_for_each_entry(provider, &of_clk_providers, link) {

if (provider->node == clkspec->np) {

hw = __of_clk_get_hw_from_provider(provider, clkspec);

if (!IS_ERR(hw))

break;

}

}

mutex_unlock(&of_clk_mutex);

return hw;

}

of_clk_providers 리스트에서 루프를 돌며 요청 노드를 찾은 후 등록된 클럭 hw를 찾아 반환한다.

__of_clk_get_hw_from_provider()

drivers/clk/clk.c

static struct clk_hw *

__of_clk_get_hw_from_provider(struct of_clk_provider *provider,

struct of_phandle_args *clkspec)

{

struct clk *clk;

if (provider->get_hw)

return provider->get_hw(clkspec, provider->data);

clk = provider->get(clkspec, provider->data);

if (IS_ERR(clk))

return ERR_CAST(clk);

return __clk_get_hw(clk);

}

클럭 hw를 반환한다.

- 코드 라인 6~7에서 (*get_hw) 후크를 호출하여 클럭 hw를 찾아 반환한다.

- 코드 라인 9~12에서 위의 후크 함수가 없으면 호환을 위해 사용되는 (*get) 후크 함수를 호출하여 클럭을 찾고, 그 클럭의 클럭 hw를 반환한다.

다음 그림은 uart 디바이스에 사용하는 클럭을 알아오는 모습을 보여준다.

__of_clk_get_from_provider()

drivers/clk/clk.c

struct clk *__of_clk_get_from_provider(struct of_phandle_args *clkspec,

const char *dev_id, const char *con_id)

{

struct of_clk_provider *provider;

struct clk *clk = ERR_PTR(-EPROBE_DEFER);

/* Check if we have such a provider in our array */

list_for_each_entry(provider, &of_clk_providers, link) {

if (provider->node == clkspec->np)

clk = provider->get(clkspec, provider->data);

if (!IS_ERR(clk)) {

clk = __clk_create_clk(__clk_get_hw(clk), dev_id,

con_id);

if (!IS_ERR(clk) && !__clk_get(clk)) {

__clk_free_clk(clk);

clk = ERR_PTR(-ENOENT);

}

break;

}

}

return clk;

}

of_clk_providers 리스트에서 루프를 돌며 요청 device_node를 찾은 후 등록된 get 후크 함수를 호출하여 clk을 찾게되면 clk를 새로 할당받아 구성한 후 반환한다.

- 코드 라인 8~10에서 of_clk_providers 리스트를 루프를 돌며 등록된 of_clk_provider 엔트리와 요청한 노드가 동일한 경우

- 코드 라인 11~21에서 clk를 새로 할당하고 알아온 clk->core->hw 정보와 인수로 받은 dev_id, con_id 등으로 구성하여 반환한다.

클럭 consumer 디바이스

클럭 consumer 할당 및 클럭과 연결

clk_hw_create_clk()

drivers/clk/clk.c

/** * clk_hw_create_clk: Allocate and link a clk consumer to a clk_core given * a clk_hw * @dev: clk consumer device * @hw: clk_hw associated with the clk being consumed * @dev_id: string describing device name * @con_id: connection ID string on device * * This is the main function used to create a clk pointer for use by clk * consumers. It connects a consumer to the clk_core and clk_hw structures * used by the framework and clk provider respectively. */

struct clk *clk_hw_create_clk(struct device *dev, struct clk_hw *hw,

const char *dev_id, const char *con_id)

{

struct clk *clk;

struct clk_core *core;

/* This is to allow this function to be chained to others */

if (IS_ERR_OR_NULL(hw))

return ERR_CAST(hw);

core = hw->core;

clk = alloc_clk(core, dev_id, con_id);

if (IS_ERR(clk))

return clk;

clk->dev = dev;

if (!try_module_get(core->owner)) {

free_clk(clk);

return ERR_PTR(-ENOENT);

}

kref_get(&core->ref);

clk_core_link_consumer(core, clk);

return clk;

}

클럭 consumer를 할당하고 클럭 core에 연결하고, 클럭을 반환한다.

- 코드 라인 11~15에서 clk 구조체를 할당하고 디바이스 정보로 초기화한다.

- 코드 라인 17~20에서 클럭에 대한 모듈이 없으면 -ENOENT 에러를 반환한다.

- 코드 라인 22에서 클럭 참조 카운터를 증가시키고, 클럭 consumer와 클럭 core를 연결한다.

- 코드 라인 24에서 클럭을 반환한다.

클럭 사용

다음 그림은 of_clk_get() 함수 이후의 호출 과정을 보여준다.

of_clk_get()

drivers/clk/clk.c

struct clk *of_clk_get(struct device_node *np, int index)

{

return __of_clk_get(np, index, np->full_name, NULL);

}

EXPORT_SYMBOL(of_clk_get);

지정한 디바이스 노드에서 부모 @index에 해당하는 클럭을 알아온다.

- np가 클럭 소스인 경우

- “clocks=” 속성이 주어진 경우 인덱스가 지정하는 부모 클럭을 알아온다.

- np가 클럭을 사용할 디바이스인 경우

- “clocks=” 속성이 주어진 경우 인덱스가 지정하는 부모 클럭을 알아온다. 없는 경우 에러

다음 그림은 부모 인덱스 값으로 부모 클럭을 알아오는 모습을 보여준다.

__of_clk_get()

drivers/clk/clk.c

static struct clk *__of_clk_get(struct device_node *np,

int index, const char *dev_id,

const char *con_id)

{

struct clk_hw *hw = of_clk_get_hw(np, index, con_id);

return clk_hw_create_clk(NULL, hw, dev_id, con_id);

}

디바이스 노드에서 부모 index 또는 @con_id(이름)로 부모 클럭을 알아온다.

- 코드 라인 5에서 @index로 지정한 부모 클럭 hw를 알아온다.

- 코드 라인 7에서 clk 구조체를 생성하고, 클럭 코어에 연동한다. 이 때 클럭 코어의 참조 카운터가 1 증가된다.

of_clk_get_hw()

drivers/clk/clk.c

struct clk_hw *of_clk_get_hw(struct device_node *np, int index,

const char *con_id)

{

int ret;

struct clk_hw *hw;

struct of_phandle_args clkspec;

ret = of_parse_clkspec(np, index, con_id, &clkspec);

if (ret)

return ERR_PTR(ret);

hw = of_clk_get_hw_from_clkspec(&clkspec);

of_node_put(clkspec.np);

return hw;

}

디바이스 노드에서 @con_id(이름) 또는 부모 @index로 부모 클럭 hw를 알아온다.

- 코드 라인 8~10에서 디바이스 노드에서 index에 해당하는 클럭 argument 값들을 알아온다.

- 코드 라인 12~15에서 클럭 argument들을 분석하여 해당 클럭 hw를 알아와서 반환한다.

of_parse_clkspec()

drivers/clk/clk.c

/**

* of_parse_clkspec() - Parse a DT clock specifier for a given device node

* @np: device node to parse clock specifier from

* @index: index of phandle to parse clock out of. If index < 0, @name is used

* @name: clock name to find and parse. If name is NULL, the index is used

* @out_args: Result of parsing the clock specifier

*

* Parses a device node's "clocks" and "clock-names" properties to find the

* phandle and cells for the index or name that is desired. The resulting clock

* specifier is placed into @out_args, or an errno is returned when there's a

* parsing error. The @index argument is ignored if @name is non-NULL.

*

* Example:

*

* phandle1: clock-controller@1 {

* #clock-cells = <2>;

* }

*

* phandle2: clock-controller@2 {

* #clock-cells = <1>;

* }

*

* clock-consumer@3 {

* clocks = <&phandle1 1 2 &phandle2 3>;

* clock-names = "name1", "name2";

* }

*

* To get a device_node for `clock-controller@2' node you may call this

* function a few different ways:

*

* of_parse_clkspec(clock-consumer@3, -1, "name2", &args);

* of_parse_clkspec(clock-consumer@3, 1, NULL, &args);

* of_parse_clkspec(clock-consumer@3, 1, "name2", &args);

*

* Return: 0 upon successfully parsing the clock specifier. Otherwise, -ENOENT

* if @name is NULL or -EINVAL if @name is non-NULL and it can't be found in

* the "clock-names" property of @np.

*/

static int of_parse_clkspec(const struct device_node *np, int index,

const char *name, struct of_phandle_args *out_args)

{

int ret = -ENOENT;

/* Walk up the tree of devices looking for a clock property that matches */

while (np) {

/*

* For named clocks, first look up the name in the

* "clock-names" property. If it cannot be found, then index

* will be an error code and of_parse_phandle_with_args() will

* return -EINVAL.

*/

if (name)

index = of_property_match_string(np, "clock-names", name);

ret = of_parse_phandle_with_args(np, "clocks", "#clock-cells",

index, out_args);

if (!ret)

break;

if (name && index >= 0)

break;

/*

* No matching clock found on this node. If the parent node

* has a "clock-ranges" property, then we can try one of its

* clocks.

*/

np = np->parent;

if (np && !of_get_property(np, "clock-ranges", NULL))

break;

index = 0;

}

return ret;

}

디바이스 노드에서 @name 또는 @index에 해당하는 phandle 및 argument 값들을 알아와서 출력 인자 @out_args에 대입해온다.

- 코드 라인 7에서 요청한 디바이스 노드부터 시작하여 최상위 노드까지 검색을 수행한다.

- 코드 라인 14~15에서 @name이 주어진 경우 해당 인덱스를 찾는다.

- 코드 라인 16~21에서 인덱스에 해당하는 phandle 및 argument 값들을 알아와서 출력 인자 @out_args에 대입해온다. 만일 찾은 경우 성공을 반환하기 위해 루프를 벗어난다.

- 코드 라인 28~32에서 못찾은 경우 부모 노드로 이동하고 재시도한다. 단 이동한 후 “clock-ranges” 속성을 발견하면 에러를 반환하기 위해 루프를 벗어난다.

clk 관련 기타 of_api 들

of_clk_set_defaults()

drivers/clk/clk-conf.c

/**

* of_clk_set_defaults() - parse and set assigned clocks configuration

* @node: device node to apply clock settings for

* @clk_supplier: true if clocks supplied by @node should also be considered

*

* This function parses 'assigned-{clocks/clock-parents/clock-rates}' properties

* and sets any specified clock parents and rates. The @clk_supplier argument

* should be set to true if @node may be also a clock supplier of any clock

* listed in its 'assigned-clocks' or 'assigned-clock-parents' properties.

* If @clk_supplier is false the function exits returnning 0 as soon as it

* determines the @node is also a supplier of any of the clocks.

*/

int of_clk_set_defaults(struct device_node *node, bool clk_supplier)

{

int rc;

if (!node)

return 0;

rc = __set_clk_parents(node, clk_supplier);

if (rc < 0)

return rc;

return __set_clk_rates(node, clk_supplier);

}

EXPORT_SYMBOL_GPL(of_clk_set_defaults);

요청한 클럭 디바이스의 부모 클럭을 설정하고 rate를 설정한다.

부모 클럭 선택

__set_clk_parents()

drivers/clk/clk-conf.c

static int __set_clk_parents(struct device_node *node, bool clk_supplier)

{

struct of_phandle_args clkspec;

int index, rc, num_parents;

struct clk *clk, *pclk;

num_parents = of_count_phandle_with_args(node, "assigned-clock-parents",

"#clock-cells");

if (num_parents == -EINVAL)

pr_err("clk: invalid value of clock-parents property at %pOF\n",

node);

for (index = 0; index < num_parents; index++) {

rc = of_parse_phandle_with_args(node, "assigned-clock-parents",

"#clock-cells", index, &clkspec);

if (rc < 0) {

/* skip empty (null) phandles */

if (rc == -ENOENT)

continue;

else

return rc;

}

if (clkspec.np == node && !clk_supplier)

return 0;

pclk = of_clk_get_from_provider(&clkspec);

if (IS_ERR(pclk)) {

if (PTR_ERR(pclk) != -EPROBE_DEFER)

pr_warn("clk: couldn't get parent clock %d for %pOF\n",

index, node);

return PTR_ERR(pclk);

}

rc = of_parse_phandle_with_args(node, "assigned-clocks",

"#clock-cells", index, &clkspec);

if (rc < 0)

goto err;

if (clkspec.np == node && !clk_supplier) {

rc = 0;

goto err;

}

clk = of_clk_get_from_provider(&clkspec);

if (IS_ERR(clk)) {

if (PTR_ERR(clk) != -EPROBE_DEFER)

pr_warn("clk: couldn't get assigned clock %d for %pOF\n",

index, node);

rc = PTR_ERR(clk);

goto err;

}

rc = clk_set_parent(clk, pclk);

if (rc < 0)

pr_err("clk: failed to reparent %s to %s: %d\n",

__clk_get_name(clk), __clk_get_name(pclk), rc);

clk_put(clk);

clk_put(pclk);

}

return 0;

err:

clk_put(pclk);

return rc;

}

부모 클럭을 선택한다.

- 코드 라인 7~11에서 “#clock-cells” 속성값을 사용하여 “assigned-clock-parents” 속성에서 phandle의 수를 알아온다. 읽어올 수 없는 경우 에러 메시지를 출력한다.

- 예) #clock-cells = <1>; assigned-clocks = <&cru PLL_GPLL>, <&cru PLL_CPLL>; -> 2 개

- 코드 라인 13~15에서 부모 수만큼 루프를 돌며 “assigned-clock-parents” 속성에서 요청한 index의 phandle 값을 알아온다.

- 코드 라인 16~22에서 알아온 phandle 값이 null이면 skip하고 에러인 경우 함수를 빠져나간다.

- 코드 라인 23~24에서 clk_supplier 값이 0 이면서 알아온 부모 노드가 요청 노드와 동일한 경우 성공(0)리에 함수를 빠져나간다.

- 코드 라인 25~31에서 clkspec으로 클럭을 알아온다.

- 코드 라인 33~36에서 “assigned-clocks” 속성에서 부모 index로 clkspec 값을 알아온다.

- 코드 라인 37~40에서 clk_supplier 값이 0 이면서 알아온 부모 노드가 요청 노드와 동일한 경우 성공(0)리에 함수를 빠져나간다.

- 코드 라인 41~48에서 clkspec 값으로 클럭을 알아온다. 검색이 실패하는 경우 경고 메시지를 출력하고 에러를 반환한다.

- 코드 라인 50~53에서 부모 클럭으로 pclk를 지정한다.

Rate 설정

__set_clk_rates()

drivers/clk/clk-conf.c

static int __set_clk_rates(struct device_node *node, bool clk_supplier)

{

struct of_phandle_args clkspec;

struct property *prop;

const __be32 *cur;

int rc, index = 0;

struct clk *clk;

u32 rate;

of_property_for_each_u32(node, "assigned-clock-rates", prop, cur, rate) {

if (rate) {

rc = of_parse_phandle_with_args(node, "assigned-clocks",

"#clock-cells", index, &clkspec);

if (rc < 0) {

/* skip empty (null) phandles */

if (rc == -ENOENT)

continue;

else

return rc;

}

if (clkspec.np == node && !clk_supplier)

return 0;

clk = of_clk_get_from_provider(&clkspec);

if (IS_ERR(clk)) {

if (PTR_ERR(clk) != -EPROBE_DEFER)

pr_warn("clk: couldn't get clock %d for %pOF\n",

index, node);

return PTR_ERR(clk);

}

rc = clk_set_rate(clk, rate);

if (rc < 0)

pr_err("clk: couldn't set %s clk rate to %u (%d), current rate: %lu\\

n",

__clk_get_name(clk), rate, rc,

clk_get_rate(clk));

clk_put(clk);

}

index++;

}

return 0;

}

요청한 클럭 디바이스의 rate를 설정한다.

- 코드 라인 10에서 요청한 노드 이하에서 “assigned-clock-rates” 속성 값들을 대상으로 루프를 돈다.

- 코드 라인 11~13에서 rate 값이 0보다 큰 경우 “assigned-clocks” 속성에서 읽은 index 번호의 부모 클럭 노드의 “#clock-cells” 값 길이 만큼의 phandle 뒤의 argument를 읽어들여 clkspec에 대입한다.

- 코드 라인 14~20에서 알아온 phandle 값이 null이면 skip하고 에러인 경우 함수를 빠져나간다.

- 코드 라인 21~22에서 clk_supplier 값이 0 이면서 알아온 부모 노드가 요청 노드와 동일한 경우 성공(0)리에 함수를 빠져나간다.

- 코드 라인 24~30에서 clkspec 값으로 클럭을 알아온다. 검색이 실패하는 경우 경고 메시지를 출력하고 에러를 반환한다.

- 코드 라인 32~37에서 클럭의 rate를 설정한다.

다음 스크립트를 보면 pwm 노드에서 사용할 클럭 소스로 clocks BCM2835_CLOCK_PWN을 지정하였고 이 클럭을 10Mhz로 설정하는 것을 알 수 있다.

arch/arm/boot/dts/bcm283x.dtsi – raspberrypi 커널 v4.9.y

clocks: cprman@7e101000 {

compatible = "brcm,bcm2835-cprman";

#clock-cells = <1>;

reg = <0x7e101000 0x2000>;

clocks = <&clk_osc>,

<&dsi0 0>, <&dsi0 1>, <&dsi0 2>,

<&dsi1 0>, <&dsi1 1>, <&dsi1 2>;

};

pwm: pwm@7e20c000 {

compatible = "brcm,bcm2835-pwm";

reg = <0x7e20c000 0x28>;

clocks = <&clocks BCM2835_CLOCK_PWM>;

assigned-clocks = <&clocks BCM2835_CLOCK_PWM>;

assigned-clock-rates = <10000000>;

#pwm-cells = <2>;

status = "disabled";

};

클럭 등록 시 사용하는 플래그

다음의 플래그들은 최상위 framework인 common clock framework에서 유효하다.

include/linux/clk-provider.h

/* * flags used across common struct clk. these flags should only affect the * top-level framework. custom flags for dealing with hardware specifics * belong in struct clk_foo * * Please update clk_flags[] in drivers/clk/clk.c when making changes here! */

#define CLK_SET_RATE_GATE BIT(0) /* must be gated across rate change */

#define CLK_SET_PARENT_GATE BIT(1) /* must be gated across re-parent */

#define CLK_SET_RATE_PARENT BIT(2) /* propagate rate change up one level */

#define CLK_IGNORE_UNUSED BIT(3) /* do not gate even if unused */

/* unused */

/* unused */

#define CLK_GET_RATE_NOCACHE BIT(6) /* do not use the cached clk rate */

#define CLK_SET_RATE_NO_REPARENT BIT(7) /* don't re-parent on rate change */

#define CLK_GET_ACCURACY_NOCACHE BIT(8) /* do not use the cached clk accuracy */

#define CLK_RECALC_NEW_RATES BIT(9) /* recalc rates after notifications */

#define CLK_SET_RATE_UNGATE BIT(10) /* clock needs to run to set rate */

#define CLK_IS_CRITICAL BIT(11) /* do not gate, ever */

/* parents need enable during gate/ungate, set rate and re-parent */

#define CLK_OPS_PARENT_ENABLE BIT(12)

/* duty cycle call may be forwarded to the parent clock */

#define CLK_DUTY_CYCLE_PARENT BIT(13)

- CLK_SET_RATE_GATE

- rate 변경 시 반드시 gate가 닫혀 있어야 한다.

- CLK_SET_PARENT_GATE

- 입력 클럭 소스(부모 클럭)를 선택 시 반드시 gate가 닫혀 있어야 한다.

- CLK_SET_RATE_PARENT

- 현재 클럭 hw가 지원하는 rate 변경이 불가능한 경우 부모에 전파(propogation) 하여 부모 클럭부터 rate를 변경하게 한다.

- CLK_IGNORE_UNUSED

- 사용하지 않아도 gate를 닫지 않는다.

- CLK_GET_RATE_NOCACHE

- 캐시된 clock rate를 사용하지 못한다.

- 참고: clk: Provide option for clk_get_rate to issue hw for new rate (2012, v3.7-rc1)

- CLK_SET_RATE_NO_REPARENT

- rate 변경 시 부모 클럭을 변경하지 못하게 한다.

- 참고: clk: add CLK_SET_RATE_NO_REPARENT flag (2013, v3.12-rc1)

- CLK_GET_ACCURACY_NOCACHE

- 캐시된 accuracy를 사용하지 못한다.

- 참고: clk: add clk accuracy retrieval support (2013, v3.14-rc1)

- CLK_RECALC_NEW_RATES

- 통지 이후에 rate가 재산출된다. (for exynos cpu)

- 참고: clk: add CLK_RECALC_NEW_RATES clock flag for Exynos cpu clock support (2015, v4.2-rc1)

- CLK_SET_RATE_UNGATE

- gate가 열린 상태에서만 rate를 변경할 수 클럭 hw를 지원한다.

- CCF는 gate가 닫혀 있는 경우 rate를 변경하기 위해 자동으로 gate를 열고 rate를 설정한 후 다시 gate를 닫는다.

- 참고: clk: add flag for clocks that need to be enabled on rate changes (2015, v4.5-rc1)

- CLK_IS_CRITICAL

- gate 제어를 할 수 없는 클럭이다.

- 참고: clk: Allow clocks to be marked as CRITICAL (2016, v4.7-rc1)

- CLK_OPS_PARENT_ENABLE

- 부모 클럭이 enable된 상태에서만 operation을 수행할 수 있는 클럭 hw를 지원한다.

- CCF는 부모 클럭이 닫혀있으면 자동으로 잠시 prepare & enable하고 이 클럭의 operation을 수행한 후 다시 disable & unprepare를 수행한다.

- 참고: clk: core: support clocks which requires parents enable (part 1) (2016, v4.8-rc1)

- CLK_DUTY_CYCLE_PARENT

- 참고: clk: add duty cycle support (2018, v4.19-rc1)

CLK_IS_ROOT (deleted)- 루트 클럭으로 부모가 없다.

- 참고: clk: Remove CLK_IS_ROOT flag (2016, v4.7-rc3)

CLK_IS_BASIC (deleted)- clk_foo()와 같은 파생 클럭이 아닌 클럭이다.

- common clock framework에 구현되어 있는 8개의 클럭 디바이스 드라이버는 모두 CLK_IS_BASIC 플래그가 설정되어 있다.

- 참고: clk: Remove CLK_IS_BASIC clk flag (2019, v5.2-rc1)

구조체

clk 구조체

drivers/clk/clk.c

struct clk {

struct clk_core *core;

struct device *dev;

const char *dev_id;

const char *con_id;

unsigned long min_rate;

unsigned long max_rate;

unsigned int exclusive_count;

struct hlist_node clks_node;

};

- *core

- 클럭 코어 포인터

- *dev

- 디바이스 포인터

- *dev_id

- 디바이스 명

- *con_id

- connection id 문자열

- min_rate

- 최소 rate

- max_rate

- 최대 rate

- exclusive_count

- 베타적 사용 카운터

- clks_node

- 클럭 코어의 clks 리스트에 연결될 때 사용되는 노드

clk_core 구조체

drivers/clk/clk.c

struct clk_core {

const char *name;

const struct clk_ops *ops;

struct clk_hw *hw;

struct module *owner;

struct device *dev;

struct device_node *of_node;

struct clk_core *parent;

struct clk_parent_map *parents;

u8 num_parents;

u8 new_parent_index;

unsigned long rate;

unsigned long req_rate;

unsigned long new_rate;

struct clk_core *new_parent;

struct clk_core *new_child;

unsigned long flags;

bool orphan;

bool rpm_enabled;

unsigned int enable_count;

unsigned int prepare_count;

unsigned int protect_count;

unsigned long min_rate;

unsigned long max_rate;

unsigned long accuracy;

int phase;

struct clk_duty duty;

struct hlist_head children;

struct hlist_node child_node;

struct hlist_head clks;

unsigned int notifier_count;